# Intelligent Schematic Input System

# **User Manual**

Issue 6.0 - November 2002

© Labcenter Electronics

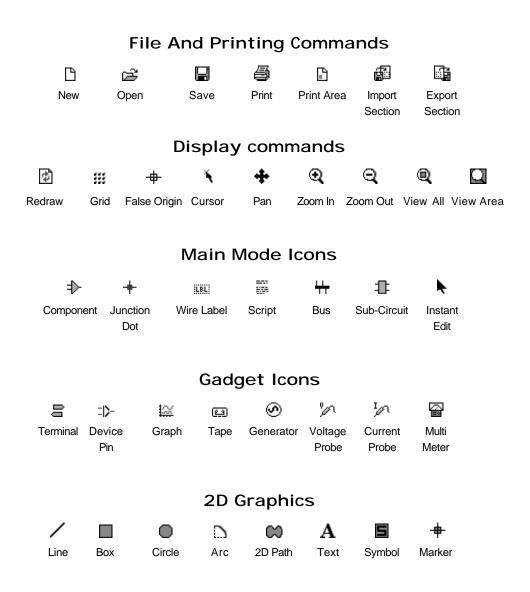

# ICON REFERENCE CHART

# TABLE OF CONTENTS

| INTRODUCTION                              | 1  |

|-------------------------------------------|----|

| ABOUT ISIS                                |    |

| ISIS AND PCB DESIGN                       |    |

| ISIS AND SIMULATION                       |    |

| ISIS AND NETWORKS                         |    |

| HOW TO USE THIS DOCUMENTATION             |    |

| TUTORIAL                                  | 5  |

| INTRODUCTION                              | 5  |

| A GUIDED TOUR OF THE ISIS EDITOR          | 5  |

| PICKING, PLACING AND WIRING UP COMPONENTS | 7  |

| LABELLING AND MOVING PART REFERENCES      | 9  |

| BLOCK EDITING FUNCTIONS                   | 10 |

| PRACTICE MAKES PERFECT                    | 10 |

| ANNOTATING THE DIAGRAM                    |    |

| The Property Assignment Tool (PAT)        | 11 |

| The Automatic Annotator                   |    |

| CREATING NEW DEVICES                      |    |

| FINISHING TOUCHES                         |    |

| SAVING, PRINTING AND PLOTTING             |    |

| MORE ABOUT CREATING DEVICES               |    |

| Making a Multi-Element Device             |    |

| The Visual Packaging Tool                 |    |

| Making Similar Devices                    |    |

| Replacing Components in a design          |    |

| SYMBOLS AND THE SYMBOL LIBRARY            |    |

| REPORT GENERATION                         |    |

| A LARGER DESIGN                           | 21 |

| GENERAL CONCEPTS2                         | 23 |

| SCREEN LAYOUT                             |    |

| The Menu Bar                              | 23 |

| The Toolbars                              |    |

| The Editing Window                        | 24 |

| The Overview Window                       | 25 |

| The Object Selector                       | 26 |

|     |           | Co-ordinate Display           |    |

|-----|-----------|-------------------------------|----|

|     | CO-ORDIN  | NATE SYSTEM                   |    |

|     |           | False Origin                  |    |

|     |           | The Dot Grid                  |    |

|     |           | Snapping to a Grid            |    |

|     |           | Real Time Snap                |    |

|     | FILING CO | OMMANDS                       |    |

|     |           | Starting a New Design         |    |

|     |           | Loading a Design              |    |

|     |           | Saving the Design             |    |

|     |           | Import / Export Section       |    |

|     |           | Quitting ISIS                 |    |

|     | GENERAL   | _ EDITING FACILITIES          |    |

|     |           | Object Placement              |    |

|     |           | Tagging an Object             |    |

|     |           | Deleting an Object            |    |

|     |           | Dragging an Object            |    |

|     |           | Dragging an Object Label      |    |

|     |           | Resizing an Object            |    |

|     |           | Reorienting an Object         |    |

|     |           | Editing an Object             |    |

|     |           | Editing an Object Label       |    |

|     |           | Copying all Tagged Objects    |    |

|     |           | Moving all Tagged Objects     |    |

|     |           | Deleting all Tagged Objects   |    |

|     | WIRING U  | JP                            |    |

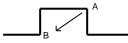

|     |           | Wire Placement                |    |

|     |           | The Wire Auto-Router          | 35 |

|     |           | Wire Repeat                   | 35 |

|     |           | Dragging Wires                |    |

|     | THE AUT   | OMATIC ANNOTATOR              |    |

|     |           | Value Annotation              |    |

|     | MISCELLA  | ANEOUS                        |    |

|     |           | The Sheet Border              |    |

|     |           | The Header Block              |    |

|     |           | Send to Back / Bring to Front |    |

| GRA | PHICS AI  | ND TEXT STYLES                |    |

|     |           | ICTION                        |    |

|     |           | L                             |    |

|     |           | Editing Global Styles         |    |

|     |           | Editing Local Styles          |    |

|     |           |                               |    |

|      | Working With The Template                      | 45 |

|------|------------------------------------------------|----|

|      | TEMPLATES AND THE TEMPLATE MENU                |    |

| PROP | ERTIES                                         |    |

|      | INTRODUCTION                                   |    |

|      | OBJECT PROPERTIES                              |    |

|      | System Properties                              |    |

|      | User Properties                                |    |

|      | Property Definitions (PROPDEFS)                |    |

|      | SHEET PROPERTIES                               |    |

|      | Introduction                                   | 49 |

|      | Defining Sheet Properties                      |    |

|      | Scope Rules for Sheet Properties               |    |

|      | DESIGN PROPERTIES                              |    |

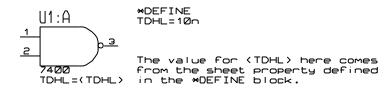

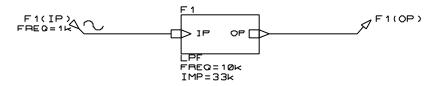

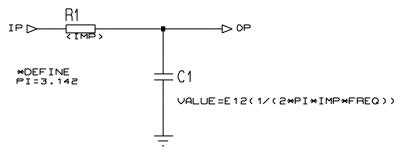

|      | PARAMETERIZED CIRCUITS                         | 51 |

|      | Introduction                                   |    |

|      | An Example                                     | 52 |

|      | Property Substitution                          | 53 |

|      | Property Expression Evaluation                 | 54 |

|      | The Rounding Functions E12 (), E24 ()          | 55 |

|      | THE PROPERTY ASSIGNMENT TOOL                   | 55 |

|      | The PAT Dialogue Form                          | 56 |

|      | PAT Actions                                    |    |

|      | PAT Application Modes                          |    |

|      | The Search and Tag Commands                    | 58 |

|      | Examples                                       |    |

|      | PROPERTY DEFINITIONS                           |    |

|      | Creating Property Definitions                  |    |

|      | Default Property Definitions                   |    |

|      | Old Designs                                    | 61 |

| OBJE | CT SPECIFICS                                   | 63 |

|      | COMPONENTS                                     | 63 |

|      | Selecting Components from the Device Libraries | 63 |

|      | Placing Components                             |    |

|      | Replacing Components                           |    |

|      | Editing Components                             | 65 |

|      | Component Properties                           |    |

|      | Hidden Power Pins                              | 66 |

|      | DOTS                                           | 66 |

|      | Placing Dots                                   | 67 |

|      | Auto Dot Placement                             | 67 |

|      | Auto Dot Removal                               | 67 |

#### LABCENTER ELECTRONICS

| 67 |

|----|

| 67 |

| 68 |

| 69 |

| 69 |

| 69 |

| 70 |

| 70 |

| 71 |

| 71 |

| 72 |

| 72 |

| 73 |

| 73 |

| 74 |

| 75 |

| 75 |

| 75 |

| 76 |

| 77 |

| 78 |

| 78 |

| 78 |

| 80 |

| 80 |

| 80 |

| 80 |

| 81 |

| 81 |

| 82 |

| 83 |

| 83 |

| 83 |

| 84 |

| 84 |

| 85 |

| 85 |

| 85 |

| 87 |

|    |

|    |

| 88 |

|    |

| Placing Markers                             |    |

|---------------------------------------------|----|

| LIBRARY FACILITIES                          |    |

| GENERAL POINTS ABOUT LIBRARIES              | -  |

| Library Discipline                          |    |

| The Pick Command                            |    |

| SYMBOL LIBRARIES                            |    |

| Graphics Symbols                            |    |

| User Defined Terminals                      |    |

| User Defined Module Ports                   |    |

| User Defined Device Pins                    |    |

| Editing an Existing Symbol                  | 96 |

| Hierarchical Symbol Definitions             |    |

| DEVICE LIBRARIES                            |    |

| Making a Device Element                     |    |

| The Make Device Command                     |    |

| The Visual Packaging Tool                   |    |

| Making a Single Element Device              |    |

| Making a Multi-Element Homogenous Device    |    |

| Making a Multi-Element Heterogeneous Device |    |

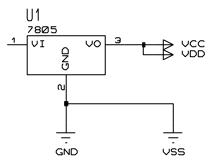

| Making a Device with Bus Pins               |    |

| Property Definitions and Default Properties |    |

| Dealing with Power Pins                     |    |

| Editing an Existing Device                  |    |

| MULTI-SHEET DESIGNS                         |    |

| MULTI-SHEET FLAT DESIGNS                    |    |

| Introduction                                |    |

| Design Menu Commands                        |    |

| HIERARCHICAL DESIGNS                        |    |

| Introduction                                |    |

| Terminology                                 |    |

| Sub-Circuits                                |    |

| Module-Components                           |    |

| External Modules                            |    |

| Moving About a Hierarchical Design          |    |

| Design Global Annotation                    |    |

| Non-Physical Sheets                         |    |

| NETLIST GENERATION                          |    |

| INTRODUCTION                                |    |

| NET NAMES                                   |    |

| DUPLICATE PIN NAMES                         |    |

|                                             |    |

| HIDDEN POWER PINS                                 |     |

|---------------------------------------------------|-----|

| SPECIAL NET NAME SYNTAXES                         |     |

| Global Nets                                       |     |

| Inter-Element Connections for Multi-Element Parts | 126 |

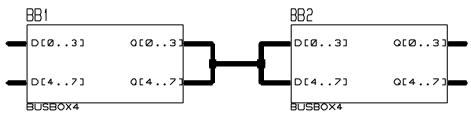

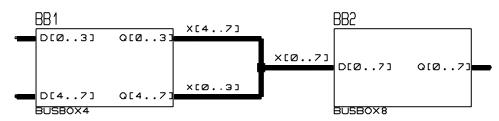

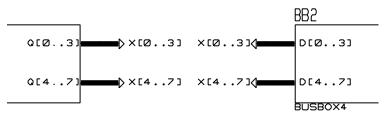

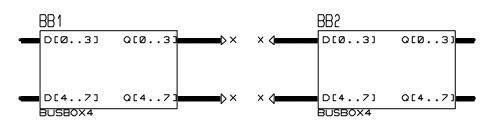

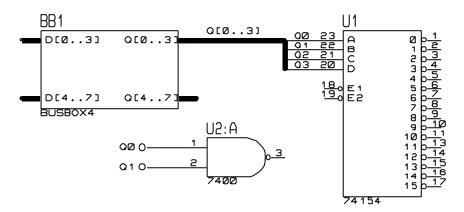

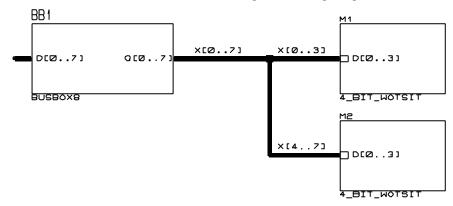

| BUS CONNECTIVITY RULES                            | 127 |

| The Base Alignment Rule                           | 127 |

| Using Bus Labels to Change the Connectivity Rule  | 127 |

| Using Bus Terminals to Interconnect Buses         | 128 |

| Connections to Individual Bits                    | 129 |

| Tapping a Large Bus                               | 131 |

| General Comment & Warning                         |     |

| GENERATING A NETLIST FILE                         | 132 |

| Format                                            |     |

| Logical/Physical/Transfer                         |     |

| Scope                                             | 132 |

| Depth                                             | 132 |

| Errors                                            |     |

| NETLIST FORMATS                                   |     |

| SDF                                               |     |

| BOARDMAKER                                        |     |

| EEDESIGNER                                        |     |

| FUTURENET                                         |     |

| MULTIWIRE                                         |     |

| RACAL                                             |     |

| SPICE                                             |     |

| SPICE-AGE FOR DOS                                 |     |

| TANGO                                             |     |

| VALID                                             |     |

| VUTRAX                                            | 134 |

| REPORT GENERATION                                 | 135 |

| BILL OF MATERIALS                                 |     |

| Generating the Report                             |     |

| Bill of Materials Configuration                   |     |

| ASCII DATA IMPORT                                 | 136 |

| The IFEND Command                                 |     |

| The DATAEND Command                               |     |

| ELECTRICAL RULES CHECK                            | 140 |

| Generating the Report                             |     |

| ERC Error Messages                                | 140 |

| HARD COPY GENERATION                              | 143 |

| PRINTER OUTPUT                                    | 143 |

|                                                   |     |

| PLOTTER OUTPUT                                             | 143 |

|------------------------------------------------------------|-----|

| Plotter Pen Colours                                        | 143 |

| CLIPBOARD AND GRAPHICS FILE GENERATION                     | 143 |

| Bitmap Generation                                          | 144 |

| Metafile Generation                                        | 144 |

| DXF File Generation                                        | 144 |

| EPS File Generation                                        | 144 |

| ISIS AND ARES                                              | 145 |

| INTRODUCTION                                               | 145 |

| PACKAGING                                                  | 145 |

| Default Packaging                                          | 145 |

| Manual Packaging                                           | 146 |

| Automatic Packaging                                        | 146 |

| Using the Bill of Materials to Help with Packaging         | 147 |

| The Package Verifier                                       | 148 |

| Packaging with ARES                                        | 148 |

| NET PROPERTIES AND ROUTING STRATEGIES                      | 148 |

| FORWARD ANNOTATION - ENGINEERING CHANGES                   | 149 |

| Adding New Components                                      |     |

| Removing Existing Components                               |     |

| Changing the connectivity                                  | 150 |

| Re-Annotating Components, and Re-Packaging Gates           |     |

| PIN-SWAP/GATE-SWAP                                         |     |

| Specifying Pin-Swaps and Gate-Swaps for ISIS Library Parts |     |

| Specifying Pin-Swaps in Single Element Devices             |     |

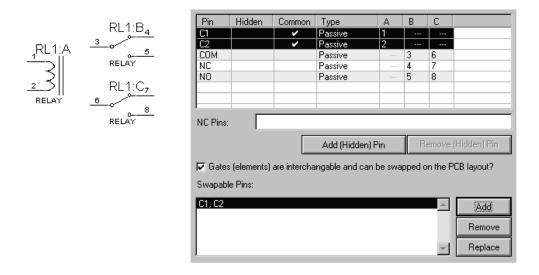

| Specifying Pin-Swaps in Multi-Element Devices              |     |

| Specifying Gate-Swaps in Multi-Element Devices             |     |

| Performing Manual Pin-Swaps and Gate-Swaps in ARES         |     |

| The Gate-Swap Optimizer                                    |     |

| RE-ANNOTATION                                              |     |

| BACK-ANNOTATION WITH ISIS                                  |     |

| Semi-Automatic Back-Annotation                             |     |

| Fully-Automatic Back-Annotation                            | 157 |

| INDEX                                                      | 159 |

# INTRODUCTION

## ABOUT ISIS

Many CAD users dismiss schematic capture as a necessary evil in the process of creating PCB layout but we have always disputed this point of view. With PCB layout now offering automation of both component placement and track routing, getting the design into the computer can often be the most time consuming element of the exercise. And if you use circuit simulation to develop your ideas, you are going to spend even more time working on the schematic.

ISIS has been created with this in mind. It has evolved over twelve years research and development and has been proven by thousands of users worldwide. The strength of its architecture has allowed us to integrate first conventional graph based simulation and now – with PROTEUS VSM – interactive circuit simulation into the design environment. For the first time ever it is possible to draw a complete circuit for a micro-controller based system and then test it interactively, all from within the same piece of software. Meanwhile, ISIS retains a host of features aimed at the PCB designer, so that the same design can be exported for production with ARES or other PCB layout software.

For the educational user and engineering author, ISIS also excels at producing attractive schematics like you see in the magazines. It provides total control of drawing appearance in turns of line widths, fill styles, colours and fonts. In addition, a system of templates allows you to define a 'house style' and to copy the appearance of one drawing to another.

Other general features include:

- Runs on Windows 98/Me/2k/XP and later.

- Automatic wire routing and dot placement/removal.

- Powerful tools for selecting objects and assigning their properties.

- Total support for buses including component pins, inter-sheet terminals, module ports and wires.

- Bill of Materials and Electrical Rules Check reports.

- Netlist outputs to suit all popular PCB layout tools.

For the 'power user', ISIS incorporates a number of features which aid in the management of large designs. Indeed, a number of our customers have used it to produce designs containing many thousands of components.

- Hierarchical design with support for parameterized component values on sub-circuits.

- Design Global Annotation allowing multiple instances of a sub-circuit to have different component references.

- Automatic Annotation the ability to number the components automatically.

- ASCII Data Import .this facility provides the means to automatically bring component stock codes and costs into ISIS design or library files where they can then be incorporated or even totalled up in the Bill of Materials report.

## ISIS AND PCB DESIGN

Users of ARES, or indeed other PCB software will find some of the following PCB design specific features of interest:

- Sheet Global Net Properties which allow you to efficiently define a routing strategy for all the nets on a given sheet (e.g. a power supply needing POWER width tracks).

- Physical terminals which provide the means to have the pins on a connector scattered all over a design.

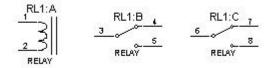

- Support for heterogeneous multi-element devices. For example, a relay device can have three elements called RELAY:A, RELAY:B and RELAY:C. RELAY:A is the coil whilst elements B and C are separate contacts. Each element can be placed individually wherever on the design is most convenient.

- Support for pin-swap and gate-swap. This includes both the ability to specify legal swaps in the ISIS library parts and the ability to back-annotate changes into a schematic.

- A visual packaging tool which shows the PCB footprint and its pin numbers alongside the list of pin names for the schematic part. This facilitates easy and error free assignment of pin numbers to pin names. In additional, multiple packagings may be created for a single schematic part.

A full chapter is provided on how to use ISIS and ARES together.

## ISIS AND SIMULATION

ISIS provides the development environment for PROTEUS VSM, our revolutionary interactive system level simulator. This product combines mixed mode circuit simulation,

micro-processor models and interactive component models to allow the simulation of complete micro-controller based designs.

ISIS provides the means to enter the design in the first place, the architecture for real time interactive simulation and a system for managing the source and object code associated with each project. In addition, a number of graph objects can be placed on the schematic to enable conventional time, frequency and swept variable simulation to be performed.

Major features of PROTEUS VSM include:

- True Mixed Mode simulation based on Berkeley SPICE3F5 with extensions for digital simulation and true mixed mode operation.

- Support for both interactive and graph based simulation.

- CPU Models available for popular microcontrollers such as the PIC and 8051 series.

- Interactive peripheral models include LED and LCD displays, a universal matrix keypad, an RS232 terminal and a whole library of switches, pots, lamps, LEDs etc.

- Virtual Instruments include voltmeters, ammeters, a dual beam oscilloscope and a 24 channel logic analyser.

- On-screen graphing the graphs are placed directly on the schematic just like any other object. Graphs can be maximised to a full screen mode for cursor based measurement and so forth.

- Graph Based Analysis types include transient, frequency, noise, distortion, AC and DC sweeps and fourier transform. An Audio graph allows playback of simulated waveforms.

- Direct support for analogue component models in SPICE format.

- Open architecture for 'plug in' component models coded in C++ or other languages. These can be electrical., graphical or a combination of the two.

- Digital simulator includes a BASIC-like programming language for modelling and test vector generation.

- A design created for simulation can also be used to generate a netlist for creating a PCB there is no need to enter the design a second time.

Full details of all these features and much more are provided in the PROTEUS VSM manual.

## ISIS AND NETWORKS

ISIS is fully network compatible, and offers the following features to help Network Managers:

- Library files can be set to Read Only. This prevents users from messing with symbols or devices that may be used by others.

- ISIS individual user configuration in the windows registry. Since the registry determines the location of library files, it follows that users can have individual USERDVC.LIB files in their personal or group directories.

## HOW TO USE THIS DOCUMENTATION

This manual is intended to complement the information provided in the on-line help. Whereas the manual contains background information and tutorials, the help provides context sensitive information related to specific icons, commands and dialog forms. Help on most objects in the user interface can be obtained by pointing with the mouse and pressing F1.

ISIS is a vast and tremendously powerful piece of software and it is unreasonable to expect to master all of it at once. However, the basics of how to enter a straightforward circuit diagram and create your own components *are* extremely simple and the techniques required for these tasks can be mastered most quickly by following the tutorial given in *Tutorial* on page 5. We strongly recommend that you work through this as it will save you time in the long run.

With some of the more advanced aspects of the package, you are probably going to find some of the *concepts* are new, let alone the details of how ISIS handles them. Each area of the software has been given a chapter of its own, and we generally start by explaining the background theory before going into the operation and use of the relevant features. You will thus find it well worthwhile reading the introductory sections rather than jumping straight to the how-to bits.

# TUTORIAL

# INTRODUCTION

The aim of this tutorial is to take you through the process of entering a circuit of modest complexity in order to familiarise you with the techniques required to drive ISIS. The tutorial starts with the easiest topics such as placing and wiring up components, and then moves on to make use of the more sophisticated editing facilities, such as creating new library parts.

For those who want to see something quickly, ISISTUT.DSN contains the completed tutorial circuit. This and other sample designs are installed to the SAMPLES directory.

# A GUIDED TOUR OF THE ISIS EDITOR

We shall assume at this point that you have installed the package, and that the current directory is some convenient work area on your hard disk.

To start the ISIS program, click on the *Start* button and select *Programs, Proteus 6 Professional*, and then the *ISIS 6 Professional* option. The ISIS schematic editor will then load and run. Along the top of the screen is the Menu Bar.

The largest area of the screen is called the *Editing Window*, and it acts as a window on the drawing - this is where you will place and wire-up components. The smaller area at the top right of the screen is called the *Overview Window*. In normal use the *Overview Window* displays, as its name suggests, an overview of the entire drawing - the blue box shows the edge of the current sheet and the green box the area of the sheet currently displayed in the *Editing Window*. However, when a new object is selected from the *Object Selector* the *Overview Window* is used to preview the selected object - this is discussed later.

You can adjust the area of the drawing displayed in the *Editing Window* in a number of ways:

- To simply 'pan' the *Editing Window* up, down, left or right, position the mouse pointer over the desired part of the *Editing Window* and press the F5 key.

- Hold the SHIFT key down and bump the mouse against the edges of the Editing Window to pan up, down, left or right. We call this *Shift Pan*.

- Should you want to move the *Editing Window* to a completely different part of the drawing, the quickest method is to simply point at the centre of the new area on the *Overview Window* and click left.

- You can also use the *Pan* icon on the toolbar.

To adjust the scale the drawing is displayed at in the *Editing Window* you can:

- Point with the mouse where you want to zoom in or out and press the F6 or F7 keys respectively.

- Press the F8 key to display the whole drawing.

- Hold the SHIFT key down and drag out a box around the area you want to zoom in to. We call this *Shift Zoom*..

- Use the Zoom In, Zoom Out, Zoom Full or Zoom Area icons on the toolbar.

A grid of dots can be displayed in the *Editing Window* using the *Grid* command on the *View* menu, or by pressing 'G', or by clicking the *Grid* icon on the toolbar. The grid helps in lining up components and wires and is less intimidating than a blank screen. If you find it hard to see the grid dots, either adjust the contrast on your monitor slightly (by default the grid dots are displayed in light grey) or change their colour with the *Set Design Defaults* on the *Template* menu.

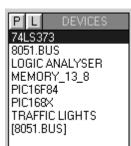

Below the *Overview Window* is the *Object Selector* which you use to select devices, symbols and other library objects.

At the bottom right of the screen is the co-ordinate display, which reads out the co-ordinates of the mouse pointer when appropriate. These co-ordinates are in 1 thou units and the origin is in the centre of the drawing.

## PICKING, PLACING AND WIRING UP COMPONENTS

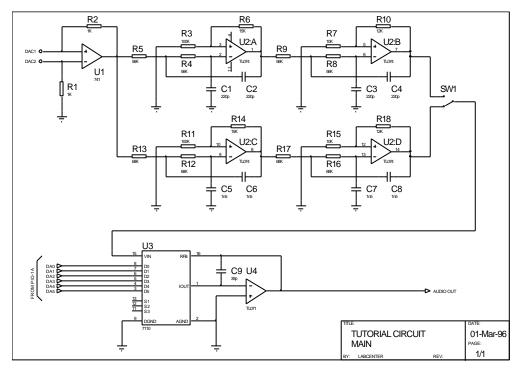

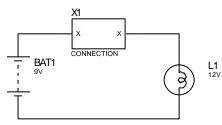

The circuit we are going to draw is shown below. It may look quite a lot to do, but some parts of it are similar (the four op-amp filters to be precise) which will provide opportunity to use the block copying facilities.

The Tutorial Circuit

We shall start with the 741 buffer amplifier comprising U1, R1, R2. Begin by pointing at the **P** button at the top left of the *Object Selector* and clicking left. This causes the *Device Library Selector* dialogue form to appear and you can now select devices from the various device libraries. There are a number of selectors labelled *Objects, Libraries, Extensions* and a *Browser*, not all of which may be shown:

• The *Library* selector chooses which of the various device libraries (e.g. DEVICE, TTL, CMOS) you have installed is current.

- The Objects selector displays all the parts in the currently selected library according to the settings in the *Extensions* selector, if it is shown (see below). Click left once on a part to browse it or double-click a part to 'pick' it in to the design.

- The *Browser* displays the last selected part in the *Parts* selector as a means of browsing the contents of the library.

We need two devices initially - OPAMP for the 741 op-amp and RES for the feedback resistors. Both these are in the DEVICE library, so, if it is not already selected, start by selecting the DEVICE library in the *Library* selector. Then, double-click on the OPAMP and RES parts from the *Parts* selector to select each part. The devices you have picked should appear in the *Object Selector*.

Whenever you select a device in the *Devices* selector or use the *Rotation* or *Mirror* icons to orient the device prior to placement, the selected device is shown previewed in the *Overview Window* with the orientation the selected device will have if placed. As you click left or right on the *Rotation* and/or *Mirror* icons, the device is redrawn to preview the new orientation. The preview remains until the device is placed or until the another command or action is performed.

Ensure the OPAMP device is selected and then move the mouse pointer into the middle of the *Editing Window*. Press and hold down the left mouse button. An outline of the op-amp will appear which you can move around by dragging the mouse. When you release the button, the component will be *placed* and is drawn in full. Place the op-amp in the middle of the *Editing Window*. Now select the RES device and place one resistor just above the op-amp as in the diagram and click left once on the anti-clockwise *Rotation* icon; the preview of the resistor shows it rotated through 90°. Finally, place the second (vertical) resistor, R1 as before.

Unless you are fairly skilful, you are unlikely to have got the components oriented and positioned entirely to your satisfaction at this first attempt, so we will now look at how to move things around. In ISIS, objects are selected for further editing by 'tagging' them. Try pointing at the op-amp and clicking right. This tags the object, causing it to be highlighted. Now, still keeping the pointer over it, hold the left button down and drag it around. This is one of the ways to move objects. Release the left button, and click right on the op-amp a second time. Clicking right on a tagged object deletes it. Select *Undo* on the *Edit* Menu (or press 'U') to recover it. Tag it again, and click first left and then right on the *Rotation* icon whilst watching the op-amp itself. The rotation of the last object tagged. Armed with the above knowledge, you should now be able to adjust the three components you have placed such that they match the diagram. When you have finished editing, point at a free space in the *Editing Window* (i.e. somewhere where there is no object) and click right to untag all tagged objects.

We can now move on to place some wires. Start by pointing at the tip of the upper end of R1 and clicking left. ISIS senses that you are pointing at a component pin and deduces that you wish to connect a wire from it. To signify this, it displays a green line which goes from the pin to the pointer. Now point at the tip of the inverting input of the op-amp and click left again. ISIS takes this as the other end for the wire and invokes the *Wire Auto Router* (WAR) to choose a route for the wire. Now do the same thing for each end of R2, following the diagram. Try tagging objects and moving them around whilst observing how the WAR re-routes the wires accordingly.

If you do not like a route that the *Wire Auto Router* has chosen, you can edit it manually. To do this, tag the wire (by pointing at it and clicking right) and then try dragging it first at the corners and then in the middle of straight runs. If you want to manually route a wire you can do so by simply clicking left on the first pin, clicking left at each point along the required route where you want a corner, and then finish by clicking left on the second pin. After a while, you will get a feel for when the WAR will cope sensibly and when you will need to take over.

To complete this first section of the drawing, you need to place the two generic and one ground terminals and wire them up. To do this, select the *Terminal* icon; the *Object Selector* changes to a list of the terminal types available. Select the *Ground* terminal, ensure its preview shows it correctly oriented, and place it just under R1. Now select the *Default* terminal from the selector and place two terminals as in the diagram. Finally wire the ground terminal to the bottom of R1 and the two default terminals to the corners of the wires going into the op-amp. ISIS will place the junction dots where required, sensing automatically that three wires are meeting at these points.

## LABELLING AND MOVING PART REFERENCES

ISIS has a very powerful feature called *Real Time Annotation* which can be found on the *Tools Menu* and is enabled by default. Full information can be found on page 11 but basically, when enabled, this feature annotates components as you place them on the schematic. If you zoom in on any resistor you have placed you will see that ISIS has labelled it with both the default value (RES) and a unique reference. To edit/input part references and values click left on the *Instant Edit* icon and then click left on the object you wish to edit. Do the resistors first, entering R1, 1k and R2, 1k as appropriate. Now do the op-amp and the two terminals. To move the 'U1' and the '741' labels to correspond with the diagram, press F2 to reduce the snapping grid to 50th (it starts off at 100th) and then tag the op-amp. Now point at the label 'U1' and with the left button depressed, drag it to its correct position under the op-amp. Then do the same with the '741' label.

When you have finished positioning the labels, put the snap back to 100th by pressing F3. Although with the *Real Time Snap* feature ISIS is able to locate pins and wires not on the

current snap grid, working consistently with the same snap grid will keep drawings looking neat and tidy.

#### **BLOCK EDITING FUNCTIONS**

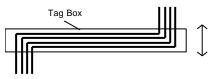

You may have noticed that the section of circuit you have drawn so far is currently located in the middle of the sheet, whereas it should be in the top left hand corner. To move it there, first tag all the objects you have placed by dragging a box round them using the right mouse button: point at a position above and to the left of all the objects; then press and hold down the right button and drag the mouse pointer to a position below and to the right of the objects. The selected area is shown by a cyan *tag-box* and (as the initial right click automatically untags any previously tagged objects) all and only those objects wholly within the *tag-box* will be tagged after the operation.

Now click left on the *Block Move* icon. A box will appear round all the tagged objects, and you can now begin to move this up towards the top left hand corner of the sheet. The sheet border appears in dark blue so you can now re-position the buffer circuit up at the top left of the drawing. Click left to effect the move, or else you can abort it by clicking right. You should also note how, when you moved the pointer off the *Editing Window* to the top or left, ISIS automatically panned the *Editing Window* for you. If you want to pan like this at other times (i.e. when *not* placing or dragging an object), you can use the *Shift Pan* feature.

The group of objects you have moved will remain tagged, so you might as well experiment with the *Copy* and *Delete* icons which similarly operate on the currently tagged objects. The effect of these icons can be cancelled by *immediately* following their use by pressing the 'U' key for Undo.

### PRACTICE MAKES PERFECT

You should be getting the hang of things now, so get some more practice in by drawing the next section of circuitry centred around the op-amp U2:A. You will need to get a capacitor (CAP). A quick method of picking devices whose names you know is to use the *Pick Device/Symbol* command. Press the 'P' key (for *Pick Device/Symbol*) and then type in the name - CAP. Use the various editing techniques that have been covered so far to get everything in the right place. Move the part reference and value fields to the correct positions, but do not annotate the parts yet - we are going to use the *Automatic Annotator* to do this.

When you have done one op-amp filter to you satisfaction, use a *tag-box* and the *Block Copy* icon to make three copies - four filters in all - as there are in the diagram. You may find it useful to use the zoom commands on the *View* menu (or their associated short-cut keys) so as

to be able to see the whole sheet whilst doing this. When you have the four filters in position, wire them together, and place a SW-SPDT device (SW1) on the drawing.

## ANNOTATING THE DIAGRAM

ISIS provides you with four possible approaches to annotating (naming) components:

- Manual Annotation This is the method you have already used to label the first op-amp and resistors. Any object can be edited either by selecting the *Instant Edit* icon and then clicking left on it, or by clicking right then left on it in the normal placement mode. Whichever way you do it, a dialogue box then appears which you can use to enter the relevant properties such as Reference, Value and so forth.

- The *Property Assignment Tool* (PAT) This tool can generate fixed or incrementing sequences and assign the resulting text to either all objects, all tagged objects (either on all sheets or the current sheet) or to the objects you subsequently click left on. Using the PAT is faster than manual annotation, though slower than using the *Automatic Annotator*. However, it does leave you in control of which names are allocated to which parts.

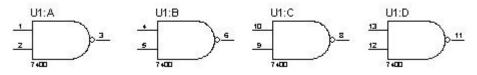

- The *Automatic Annotator* Using the *Automatic Annotator* leads to the whole design being annotated in a matter of seconds. The tool is aware of multi-element parts like the 7400 TTL NAND gate package and will allocate gates appropriately. However, the whole process is non-interactive so you get far less control over the names that are allocated than with the other two methods.

- Real Time Annotation This feature, when enabled, will annotate components as you place them on the design , obviating any need for you to place references and values in your design. As with the *Automatic Annotator*, however, it makes the whole process non-interactive and offers no user control over the annotation process. *Real Time Annotation* can be toggled on and off through the *Real Time Annotation* command on the *Tools* Menu or via the CTRL + N shortcut key.

In practice you can use a mix of all four methods, and in any order you choose. The *Automatic Annotator* can be set to leave alone any existing annotation so that it is possible to fix the references of certain parts and then let ISIS annotate the rest by itself. As the *Real Time Annotation* is enabled by default, we shall leave it on and use the other three methods to edit the existing annotation of the design.

#### The Property Assignment Tool (PAT)

Let us suppose, for the sake of argument, that you wished to pre-annotate all the resistors using the PAT. Given that you have already manually annotated R1 and R2, you need to generate the sequence R3, R4, R5 etc. To do this, select the *Property Assignment Tool* option

#### LABCENTER ELECTRONICS

on the *Tools* menu. Enter REF=R# in the *String* field, then move the cursor to the next field (the *Count* field) and key in the value 3. Ensure the *On Click* button is selected and then click left on the *OK* button or press ENTER. The hash-character ('#') in the *String* field text will be replaced with the current *Count* field value each time the PAT assigns a string to an object and then the *Count* field value is incremented.

ISIS automatically selects the *Instant Edit* icon so that you can annotate the required objects by clicking left on them. Point at resistor R3 and click left. The PAT supplies the R3 text and the part is redrawn. Now do the same for the resistor below it, R4 and see how the PAT's *Count* field value increments each time you use it. You can now annotate the rest of the resistor references with some panache. When you are done with this, cancel the PAT, by calling up its dialogue form (use the 'A' keyboard shortcut for speed) and then either clicking on the CANCEL button or by pressing ESC.

The PAT can also be used to assign the same *String* to several tagged objects, for example the part values of resistors or capacitors that all have the same value. Consider the capacitors C1 to C4 which all have the value 220p. To assign this value, first ensure that only the capacitors are tagged by first clicking right on a free area of the *Edit Window* to untag all objects, then clicking right on each capacitor. Now invoke the PAT and enter VAL=220p in the *String* field, select the *Local Tagged* button and click OK. That's it - you do not need to cancel the PAT as it is not in its 'On Click' assignment mode.

Try this on your own for the rest of the diagram until you are clear about how the PAT works - although a little tricky at first, it is an extremely powerful tool and can eliminate a great deal of tedious editing. Do not forget that, when used in its *On Click* mode, you need to cancel the tool when finished.

#### The Automatic Annotator

ISIS features an automatic annotator which will choose component references for you. It can be made to annotate all the components, or just the ones that haven't yet been annotated - i.e. those with a '?' in their reference.

Since you have already annotated some of the parts, we will run the *Automatic Annotator* in 'Incremental' mode. To do this, invoke the *Global Annotator* command on the *Tools* menu, click on the *Incremental* button, and then click on OK. After a short time, the diagram will be re-drawn showing the new annotation. Since the OPAMP device is not a multi-element part like a true TL074, the annotator annotates them as U2 to U5 which is not what is wanted. To correct this, edit each one in turn and key in the required reference. We will see how to create and use a proper TL074 later on.

Even with the automatic annotator, you still have to set the component values manually, but try this for speed - instead of moving around the drawing to edit each component in turn, simply key 'E' for *Edit Component* (on the *Edit* menu) and key in a component's reference.

This automatically locates the desired part and brings up its *Edit*... dialogue form. You should also try out the using the *Property Assignment Tool* as described in the above section.

### **CREATING NEW DEVICES**

The next section of the circuit employs a 7110 digital attenuator, and this provides an opportunity to learn how to make new devices in ISIS.

In ISIS new devices are created directly on the drawing - there is no separate device editor mode, let alone a separate program. The new device is created by placing a collection of 2D graphics and pins, annotating the pins, and then finally tagging them all and invoking the *Make Device* command.

You will find it helpful when creating new devices to sketch out on paper how you want the device to look, and to establish roughly how big it needs to be by considering how may pins there will be down each side and so on. In this case you can use the diagram opposite as a guide. The first thing we need to do is to locate a free area of your design where the new device can be created - click the left mouse button on the lower-right region of the *Overview Window* to position the *Editing Window* on that area of the design.

Begin by drawing the device body of the new device. Select the *Box* icon. You will see that the *Object Selector* on the right displays a list of *Graphics Styles*. A graphics style determines how the graphic we are about to draw will appear in terms of line colour, line thickness, fill style, fill colour, etc. Each style listed is a different set of such attributes and define the way different parts of the schematic appear.

ISIS supports a powerful graphics style system of local and global styles and the ability of local styles to 'follow' or 'track' global styles that allows you to easily and flexibly customise the appearance of your schematic. See the section *Graphics And Text Styles* on page 41 for a complete explanation of how styles work and how they are used.

As we are drawing the body of a component, select the *COMPONENT* graphics style and then place the mouse pointer over the *Editing Window*, press and hold down the left mouse button and drag out a rectangle. Don't worry about getting the size exactly right - you can always resize the rectangle later. You will see that, as a result of choosing the *COMPONENT* graphics style, the rectangle appears in the same colour, fill, etc. as all the other components on the schematic.

The next thing to do is to place the pins for the new device. To do this, first select the the *Device Pin* icon. The *Object Selector* lists the types of available pins (note that you can also

create your own pin objects in ISIS, though we will not cover that in this tutorial). Select the *Default* pin type from the selector; the *Overview Window* provides a preview of the pin with the pin's name and number represented by the strings NAME and 99 and its base and end indicated by an *Origin* marker and cross respectively - the cross represents the end to which you will eventual connect a wire. Use the *Rotation* and *Mirror* icons to orient the pin preview ready to place the left-hand pins and then click the left mouse button in the *Editing Window* on the left edge of the rectangle where you want each pin's base to appear. Place pins for the VIN, D0..D5, S1..3 and DGND pins. Note that you can use the DOWN key to move the mouse pointer down one grid square and the ENTER key as a substitute for the left on the *Mirror* icon and then place the three right-hand pins: RFB, IOUT and AGND. To finish, place two pins, one on the top edge and one on the bottom edge of the rectangle, adjusting the *Rotation* and *Mirror* icons before placing them in order that they point outwards from the device body; these pins will be the VDD and VBB power pins and will eventually be hidden (this is why they are not shown in the figure).

At this stage, you can reposition the pins or resize the rectangle as required. To move a pin, tag it with the right mouse button and then drag it with the left button; to re-orient it, use the *Rotation* and *Mirror* icons. To adjust the size of the device body rectangle, tag it with the right mouse button, click and hold down the left mouse button on one of the eight 'drag handles' (the small white boxes at the corners and mid-points of the rectangle's edges) and drag the handle to the new position. If you adjust its width, you will also need to draw a *tagbox* (with the right mouse button) around the pins and then use the *Move* icon to re-position them.

So, having arranged the device body rectangle and pins as required, we now need to annotate the pins with names and numbers, and to assign them an electrical type. The electrical type (input, power, pull-up, etc.) is used by the *Electrical Rules Check* to ensure that only pins with the correct electrical type are inter-connected.

We will first assign names, electrical types and visibility. To do this, we have to tag each pin by clicking right on it and then edit it by clicking left on the tagged pin; the pin displays its *Edit Pin* dialogue form.

Edit each pin in turn, as follows:

- Enter the pin's name in the *Name* field. Leave the *Number* field empty as we will assign the pin numbers with the *Property Assignment Tool*.

- Select the appropriate electrical type for the pin *Output* for the IOUT pin, *Power* for the VDD, VBB, AGND and DGND pins, and *Input* for the remainder.,

- Select whether the pin is to be hidden by unchecking its *Draw body* checkbox the VDD and VBB pins are both standard power pins and can be hidden. The AGND and

DGND pins are non-standard and so need to remain visible in order that they can be wired up as appropriate to the design the device is being used in.

• Select the OK button when finished.

To assign the pin numbers, we will use the *Property Assignment Tool*. To initialise the PAT, select the *Property Assignment Tool* command from the *Tools* Menu, and enter NUM=# in the *String* field and the value 1 in the *Count* field. Select the *On Click* button, and then close the dialogue form with the OK button. Now carefully click on each pin in order of its number (IOUT, AGND, etc.). As you click on each pin, it is assigned a pin number by the PAT. When done, don't forget to cancel the PAT by bringing up its dialogue form and selecting the CANCEL button.

All we do now is actually make the device. To do this, tag all the pins and the body rectangle - the easiest way is to drag out a tag-box with the right mouse button around the whole area being careful not to miss out the two hidden power pins. Finally, select the *Make Device* command from the *Library* menu to display the *Make Device* dialogue form. Key in the name 7110 in the *Name* field and the letter U in the *Prefix* field. Then press the *Next* button until the list of writable device libraries is displayed, select an appropriate library and then click the OK button to save the new device.

## FINISHING TOUCHES

Now that you have defined a 7110 you can place, wire up and annotate the remainder of the diagram - use the *Automatic Annotator* in Incremental mode to annotate the new parts without disturbing the existing annotation.

The labelling and bracket around the six input terminals DA0-DA5 is done with 2D graphics. ISIS provides facilities for placing lines, boxes, circles, arcs and text on your drawings; all of which offered as icons on the *Mode Selector* toolbar.

The bracket is made from three lines - place these by selecting the *Line* icon and then clicking at the start and end of each line. Then place the text FROM PIO-1A as shown by selecting the *Text* icon, setting the *Rotation* icon to 90° and then clicking left at the point where to want the bottom of the 'F' character to appear. You can of course tag and drag 2D graphics objects around to get things just how you want.

Finally, you need to place a sheet border and a header block. To do the former, select the *Box* icon, zoom out till you can see the whole sheet outline (dark blue) and then place a graphics box over it. It is important to realise that the dark blue sheet outline does <u>not</u> appear on hard copy - if you want a bounding box you must place one as a graphics object.

The header block is worthy of more discussion. It is, in fact, no different from other symbols such as you might use for your company logo (see section [Symbols And The Symbol

*Library*] for more on symbols). A default header block called HEADER is provided but you can re-define this to suit your own requirements - see *The Header Block* on page 38.

To actually place the header, select the *Symbol* icon and then click left on the **P** button of the *Object Selector* to display the *Symbol Library Selector* dialogue form. Picking symbols from symbol libraries is similar to picking devices from device libraries except that there is no *Prefix* selector. Select the HEADER object from the SYSTEM symbol library and close down the dialogue form. With HEADER now the current symbol, point somewhere towards the bottom left of the drawing, press the left mouse button, and drag the header into position.

Some of the fields in the header block will fill in automatically; others such as the Design Title, Sheet Title, Author and Revision need to be entered using the *Edit Design Properties* and *Edit Sheet Properties* commands on the *Design* menu. Note that the *Sheet Name* field on the *Edit Sheet Properties* dialogue form is different from the *Sheet Title* - the *Sheet Name* is a short label for the sheet that is used in hierarchical design. The *Sheet Title* is a full description of the circuitry on that sheet and it is this that will appear in the header block.

You will need to zoom in on the header to see the full effects of your editing.

## SAVING, PRINTING AND PLOTTING

You can save your work at any time by means of the *Save* command on the *File* menu, and now is as good a time as any! The *Save As* option allows you to save it with a different filename from the one you loaded it with.

To print the schematic, first select the correct device to print to using the *Printer Setup* command on the *File* menu. This activates the Windows common dialogue for printer device selection and configuration. The details are thus dependent on your particular version of Windows and your printer driver - consult Windows and printer driver documentation for details. When you have selected the correct printer, close the dialogue form and select the *Print* option on the *File* menu to print your design. Printing can be aborted by pressing ESC, although it may be a short time before everything stops as both ISIS and possibly your printer/plotter have to empty their buffers.

Further details regarding printer and graphics output are given under *Hard Copy Generation* on page 143.

If you have the demo version, please note that you can only print un-modified sample designs. To try this now, use the Load command on the File menu to load a sample design.

### MORE ABOUT CREATING DEVICES

#### Making a Multi-Element Device

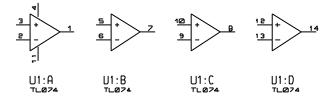

We shall now define a proper library part for the TL074 quad op-amp. As there are four separate op-amps to a single TL074 package our tutorial will be showing you how to create *multi-element devices* using the *Visual Packaging Tool*.

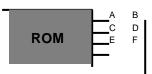

The illustration on the left shows the new op-amp device before it is made. The op-amp is made from some 2D graphics, five pins and an origin marker. We will look at two ways to construct the op-amp graphics. The easiest approach uses the pre-defined OPAMP symbol. Proceed as follows:

- Click on the *Symbol* icon and then click the **P** button at the top left of the *Symbols Object Selector*. This will launch the *Symbol Library Selector* dialogue form.

- Double-click on OPAMP in the *System* Library and close the dialogue form using the Windows *Minimise* button on the right of the title bar.

- Position the mouse pointer in an empty area of the *Editing Window* and use the left mouse button to place the op-amp. The op-amp automatically appears in the *COMPONENT* graphics style as this style was used to create the symbol.

Now place the pins around the component body. This is the same process as for creating the 7110 attenuator earlier:

- Select the *Device Pin i* con to obtain a list of available pin types and select the *Default* type.

- Use the *Rotate* and *Mirror* icons to orient the pins before placing them on the design.

- Once all the pins are in the correct positions, edit each pin in turn by tagging it with the right mouse button and then clicking left on it. Use the resulting *Edit Pin* dialogue form to annotate the pin with the correct electrical type and pin name. We have to give the pins names so that we can reference them in the *Packaging Tool* however, we don't want the name to be displayed (as the op-amp pins' uses are implicit from the graphics) so ensure that the *Draw Name* check-box is <u>not</u> checked. Note, there is no need to specify pin numbers as these will entered using the *Packaging Tool*.

The power pins have the names V+ and V- and have the electrical type of *Power*; if you place them just in from the left edge of the op-amp, you will find they just touch the sloping sides of the OPAMP graphic whilst keeping their pin ends (marked by an 'X') on a grid-square. If in a similar situation, they didn't touch, you could 'extend' the base of the pin by placing short lines in 2D Graphic Mode and with the mouse snap off. The input pins have the names +IP and -IP and the electrical type *Input*. The output pin has the name OP and the electrical type *Output*.

#### LABCENTER ELECTRONICS

The final stage is to place an *Origin* marker. Select the *Marker* icon to display a list of system marker symbols in the *Object Selector*. Select the *Origin* marker in the *System Library* and then place the marker symbol at the centre of the op-amp graphics. The *Origin* marker is displayed as a rectangle with cross-hairs and it indicates to ISIS how the new device should appear around the mouse pointer when the device is dragged or placed in a design.

We have now completed making the device. Tag the constituent parts - the op-amp symbol, pins and the *Origin* marker - by dragging out a *tag-box* around them using the right mouse button, and then invoke the *Make Device* command on the *Library* menu. Then proceed as follows:

- Enter the Device Name as TL074 and the Prefix as 'U'

- Click *Next* button display the *Packaging* page and click *Add/Edit* to launch the packaging tool itself.

#### The Visual Packaging Tool

The visual packaging tool provides a graphical environment in which to assign one or more PCB footprints to a schematic part. For each packaging, a table of pin numbers to pin names is created such that different packagings can have different pin numbers for the same schematic pin.

Having launched the packaging tool, the first thing to do is to create a packaging:

- Click the Add button. This will launch the ARES library browser.

- Select the PACKAGE library, and double click the DIL14 part.

Then, you need to make the following changes to the default settings for the packaging:

- Change the number of elements from 1 to 4. This corresponds with the fact that there are four op-amps within the one physical DIL14 package.

- Mark the V+ and V- pins as common pins. This means that they will have the same pin number on each element, and that you can wire to any or all of the pins on the elements on the schematic. All such wiring will be deemed interconnected.

- Click the *Gates can be Swapped* checkbox. This specifies that the elements are identical and the ARES can perform gateswap operations on this part.

| isis Pack                                  | ,                                                                         |                      | age? Add                 | <u>R</u> er | name | Dek | ete | ▼<br><u>O</u> rder |   |            |         | 1      | ?× |

|--------------------------------------------|---------------------------------------------------------------------------|----------------------|--------------------------|-------------|------|-----|-----|--------------------|---|------------|---------|--------|----|

| Pin                                        | Hidden                                                                    | Common               | Туре                     | A           | В    | С   | D   |                    |   | •          | $\sim$  | 14     |    |

| +IP<br>-IP                                 |                                                                           |                      | Input<br>Input           |             |      |     |     |                    |   | 2          |         | 13     |    |

| 0P<br>V+<br>V-                             |                                                                           | <b>v</b><br><b>v</b> | Output<br>Power<br>Power |             |      |     |     |                    |   | 3          |         | (2     |    |

|                                            |                                                                           |                      |                          |             |      |     |     |                    |   | 4          |         | 0      |    |

| NC Pins:                                   | : I_                                                                      |                      |                          |             | -ar  |     |     |                    |   |            |         |        |    |

| Add (Hidden) Pin Remove (Hidden) Pin (5)   |                                                                           |                      |                          |             |      |     |     |                    |   |            |         |        |    |

|                                            | Gates (elements) are interchangable and can be swapped on the PCB layout? |                      |                          |             |      |     |     |                    |   |            |         |        |    |

| Swapab                                     | Swapable Pins:                                                            |                      |                          |             |      |     |     |                    |   |            |         |        |    |

|                                            |                                                                           |                      |                          |             |      |     |     |                    |   |            |         |        |    |

| Remove Replace                             |                                                                           |                      |                          |             |      |     |     |                    |   |            |         |        |    |

| Shows the ARES package currently selected. |                                                                           |                      |                          |             |      |     |     |                    |   |            |         |        |    |

|                                            |                                                                           |                      | enity selected.          |             |      |     |     |                    |   |            |         |        | _  |

| V Use A                                    | ARES Librar                                                               | les                  |                          |             |      |     |     |                    | A | ssign Pacl | kage(s) | Cancel |    |

You should then see a display similar to that below:

Now to assign the pin numbers. The actual pinning of the op-amps that we are aiming at is shown below:

Proceed as follows:

- Click left in the 'A' column box for pin +IP.

- Either, click pin '3' on the package display or enter '3' from the keyboard and press TAB. Either way, pin '3' will highlight on the package to show that you have assigned it, and the cursor will move to the -IP row.

• Now, repeat the process for the other pin numbers, until all the pins on the package display are highlighted. This of course, provides a visual cue that you haven't missed any pins.

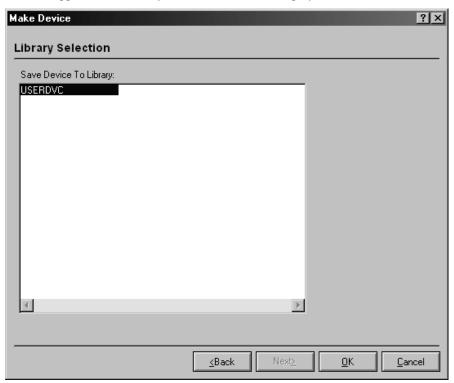

Finally, click the *Assign Packages* button to return the *Make Device* wizard, and then store the device into your USERDVC library, as you did with the 7110.

There is, as you have probably realized, a great deal of functionality built into the packaging tool. For a detailed discussion and further examples, see *DEVICE LIBRARIES* on page 96.

#### Making Similar Devices

Having defined a TL074, you can almost instantly define types TL064 and TL084 as well. Simply place a TL074, tag it, and invoke the *Make Device* command; change the name to TL064 (or whatever) and save it. What could be simpler? If you needed to add something to the basic TL074 - perhaps some more graphics, you could simply add them on top of the placed TL074 before invoking the *Make Device* command. Alternatively, if the TL074 was almost right but needed some slight editing before it was suitable for the new device, you could decompose it back into its constituent parts by tagging it, selecting the *Decompose* command on the *Library* menu, editing and/or adding to them, and then making the new device.

#### Replacing Components in a design

You can now replace the four filter op-amps and with proper TL074 parts. To replace a component with one of a similar type, pick the new device, ensure the mouse is over the device you want to replace, click and hold down the left mouse button and drag the new device such that one or more pin-ends overlap. ISIS will then transfer the wires from the old component to the new component whilst keeping all other information about the old component (e.g. its reference, etc.) intact.

### SYMBOLS AND THE SYMBOL LIBRARY

Tag the three lines that form the bracket around the inputs to the 7110. Then invoke *Make Symbol* on the *Library* menu, key in TEST for the symbol name and press ENTER. Now select the *Symbol* icon. You will see that the item TEST has appeared in the *Object Selector*. Pick this and try placing it on the drawing. Common uses for this are things like OPAMP, which is needed for many device types, and logos, emblems etc.

A special use of symbols is for the HEADER block. The default symbol was created out of 2D lines, a box and several special text primitives that are automatically replaced by properties associated with the current design and sheet. For example, a text object with the string:

@DTITLE

will automatically appear as the design title entered in the *Edit Design Properties* command's dialogue form. The complete list of keywords is presented in *The Header Block* on page 38.

## **REPORT GENERATION**

Now that the diagram is complete, you can generate Netlist, Bill of Materials (BOM) and Electrical Rules Check (ERC) reports from it. Each report is generated by invoking the appropriate command from the *Tools* menu. The report output is displayed in a pop-up text viewer window from where it can be saved to a file by selecting the 'Save as' button or placed on the clipboard for use in other packages using the 'Copy to clipboard' button; the 'Close' button clears the report display and returns you back to the editor. Note that the last report or simulation log generated is maintained by ISIS - to view a report again, select the *Text Viewer* command on the *System* menu.

The Bill of Materials report should be fairly self explanatory, although you can get a lot more out of the facility - see *Bill Of Materials* on page 135.

The Electrical Rules Check report will contain quite a few errors, since the tutorial circuit is not a complete design - of particular note is that the VBB pin of the 7110 is flagged as undriven, which could easily be forgotten in a real situation.

Further information regarding Report Generation is given in *Report Generation* on page 135 whilst *Netlist Generation* on page 123 details in intricacies of producing and using a netlist. For those of you who have bought ISIS to use with ARES, details of how to link the two packages together are provided in *Isis And Ares* on page 145.

# A LARGER DESIGN

In this last section, we shall take a look at a pre-prepared design - EPE.DSN. This is a multi-sheet, hierarchical schematic for micro-processor controlled EPROM programmer/emulator (EPE). As such, it represents a substantial piece of electronics at the lower end of design complexity that you might expect to design with your ISIS system.

The EPE design is structured as three A3 sheets (Processor, Emulator and PSU). Sub-sheets are used to represent an Emulation RAM bank (of which there are 4, giving 32 bit emulation capability) and a Programmable Power Supply (PPSU) of which 6 are required to deal with the range of 27 series EPROM pinouts.

Load the design into ISIS by using the *Load* command on the *File* menu, and then selecting EPE.DSN from the file selector. You will find it in the "Samples\Schematic & PCB Design" folder of your Proteus installation. Alternatively, you can view any of the sample designs by launching the SAMPLES help file from the *Help* menu.

#### LABCENTER ELECTRONICS

The first sheet is the CPU - take a look round this with the usual pan and zoom facilities. Then, to see more of the design, invoke the *Goto Sheet* command on the *Design* menu. Select the second item from the selector and after some disk activity the Emulator Control sheet will be loaded. Zoom out so that you can see all of it. The 4 big blue boxes are the sub-circuits. The labelling text at the top is the sub-circuit ID (like a part reference) and the text at the bottom is the circuit name.

You can also zoom into the sub-circuits: point at one of the sub-circuits and press the CTRL and 'C' keys together (C is a short-hand for *Child*). ISIS swaps out the Emulator Control sheet and loads an ERAM bank sheet. Take a look round the ERAM bank circuit and in particular, take note of a few of the component numbers. To get out, press the CTRL and 'X' keys together. Zoom into another ERAM bank and compare the component numbers in this one with the first - although both sub-circuit instances share the same circuit (if you modify one instance of the circuit, this will be instantly reflected in the others which simplifies design modification) each has its own set of component annotations; this is *Design Global Annotation* at work.

Now that you know about loading the various sheets and hierarchy roaming you may as well explore the rest of the EPE design. It is a good mix of analogue, digital and microprocessor circuits which shows how ISIS is well suited to all types of schematic.

# **GENERAL CONCEPTS**

### SCREEN LAYOUT

#### The Menu Bar

<u>File View Edit Library Tools Design Graph Source Debug Template System Help</u>

The *Menu Bar* runs across the top row of the screen and its main purpose (the selection of commands from the menus) is the same as with any other Windows application. In addition, the title bar area above the menu names is used to display certain prompt messages which indicate when the program has entered a particular editing or processing mode.

#### The Toolbars

As with other modern Windows applications, ISIS provides access to a number of its commands and modes through the use of toolbars. The toolbars can be dragged to any of the four edges of the ISIS application window.

#### **Command Toolbars**

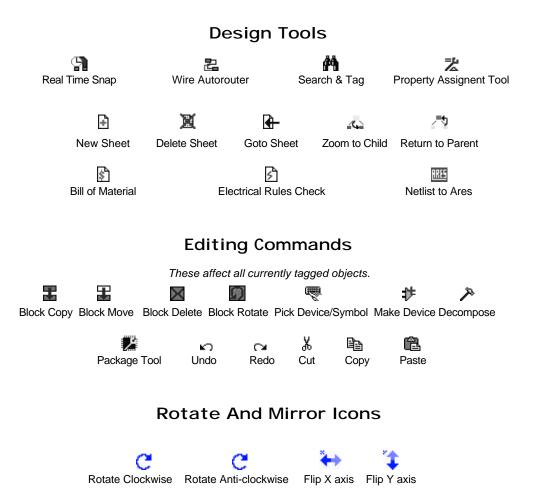

The tools located along the top of the screen (by default) provide alternative access to the menu commands, as follows:

| File/Print commands | D 🖒 🖫 📾 📾 🎒 D                                    |

|---------------------|--------------------------------------------------|

| Display Commands    | 🖉 🏢   🖶   💠 Q, Q, Q, Q, 🖸                        |

| Editing Commands    | ちょうなる 四日回    1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| Design Tools        | [] 윤 씨 값 🛛 🖉 🕒 🗸 🗥 🚯 🕅                           |

If you are working on a relatively small monitor, you can hide any or all of the command toolbars using the *Toolbars* command on the *View* menu.

#### Mode Selector Toolbar

Main Modes

The toolbar located down the left hand edge of the screen select the editor mode, i.e. what happens when you click the mouse on the *Editing Window*.

#### LABCENTER ELECTRONICS

Note that the mode toolbar cannot be hidden, as its functions are not duplicated on the menus.

#### **Orientation Toolbar**

The orientation toolbar displays and controls the rotation and reflection for objects placed onto the layout.

The edit box allows you type a rotation angle in directly; but note that in ISIS, only orthogonal angles may be entered.

When an existing object is tagged, the rotation and reflections icons highlight in red to show that they will modify the orientation of an object on the layout. When the icons are not highlighted, they serve to determine the orientation for new objects.

#### The Editing Window

The *Editing Window* displays the part of the schematic that you are currently editing. The contents of the *Editing Window* may be redrawn using the *Redraw* command on the *View* menu. This also redraws the *Overview Window*. You can use this feature after any other command that has left the display somewhat untidy.

#### Panning

You can reposition the *Editing Window* over different parts of the design in several ways:

- By clicking left at a point on the *Overview Window* this re-centres the *Editing Window* about the marked point.

- By moving the mouse over the *Editing Window*, holding down the SHIFT key, and 'bumping' the pointer against one of its edges. This pans the display in the appropriate direction. We refer to this feature as *Shift-Pan*.

- By pointing in the *Editing Window* and pressing the Zoom key (see below). This recentres the display about the cursor position.

• By using the *Pan* icon on the toolbar.

#### Zoom In / Zoom Out

You can magnify or reduce the display of the board using the *Zoom In* and *Zoom Out* commands which are also invoked by the F6 and F7 shortcut keys. Pressing F8 will display a view of the entire board. You can also use the corresponding icons on the toolbar.

If the keyboard is used to invoke the command, then the *Editing Window* will be redrawn to display a region centred around where the mouse cursor was pointing before. This also provides a way to effect a pan by pressing the zoom key for the current level and simultaneously pointing with the mouse at where you want centre of the new display to be.

#### Variable Zoom

An arbitrary degree of magnification can be achieved using the Shift-Zoom feature. A given area of the board can be selected to fill the *Editing Window* by holding down the SHIFT key, pressing the left mouse button and dragging out a box around the desired area. The area can be marked on either the *Editing Window* or the *Overview Window*.

You can also zoom to an area by clicking the Zoom Area icon on toolbar.

# The Overview Window

This window normally shows a simplified representation of the whole drawing, and has a half-inch grid on it. The cyan box marks the outline of the sheet border, whilst the green box indicates the area of the design currently visible in the *Editing Window*.

Clicking left at a point on the grid re-centres the *Editing Window* around this point, and redraws the *Editing Window*.

an object that is selected for placement. This *Place Preview* feature is activated in the following circumstances for any object which may be oriented:

- When an object is selected from the object selector.

- When the rotate or mirror icons are adjusted.

- When an object type icon is selected for an object whose orientation can be set (e.g. the *Component* icon, *Device Pin* icon, etc.).

The place preview display is cleared automatically as soon as you proceed the place the object, or when you perform any operation other than those listed above.

The width and height of the *Overview Window* can be adjusted by dragging its borders. If you drag the vertical border right over to the other side of the application Window, ARES will re-organize the display so that the *Overview Window* and *Object Selector* are located at the right hand side.

#### The Object Selector

The Object Selector is used for picking components, terminals, generators, graph types and so on from those that are available. It always carries a label indicating what it is listing and this serves as a prompt additional to the state of the Icon Panel as to which mode is current.

The width and position of the *Object Selector* can be adjusted in conjunction with the width and height of the *Overview Window*, as described above.

The buttons at the top left of the object selector activate various functions such as library browsing and library management. The exact functions available depend on the current editor mode.

#### **Co-ordinate Display**

The current co-ordinates of the mouse pointer are displayed down at the bottom right of the screen by default. The read-out can be in imperial or metric units and a false origin may be set. Further details are given under CO-ORDINATE SYSTEM on page 26.

The *X*-*Cursor* command will display a small or large cross, in addition to the mouse arrow, at the exact location of the current co-ordinates. This is particularly helpful when used in conjunction with the Real Time Snap feature, since it gives you an immediate indication of what ARES thinks you are pointing at.

# **CO-ORDINATE SYSTEM**

All co-ordinates in ISIS are actually held in 10nm units, purely to be consistent with ARES. However, the coordinate read-out is restricted to 1 thou units. The origin is held to be in the centre of the work area and so both positive and negative values are used. The co-ordinates of the pointer are displayed at the bottom right of the screen.

We refer to a 1 thou increment as a unit.

# False Origin

Although the *Origin* command appears on the *View* menu, it should only be used via its keyboard short cut (key 'O'). Its function is to zero the co-ordinate display at the current mouse position, a feature that is most useful when laying out a complex pattern of pads given a set of dimensions on a drawing of the component.

When a false origin is set, the co-ordinate display changes colour from black to magenta as a reminder.

Cancelling a false origin is done by invoking the Origin command a second time.

# The Dot Grid

A grid of dots is displayed in the *Editing Window* - this can be toggled on and off using the *Grid* command on the *View* menu. The dot spacing reflects the current snap setting., unless this would result in a ridiculous number of dots, in which the spacing is increased.

# Snapping to a Grid