# **THB8128 Development Specification Proposal**

- 1. Application: PWM current control stepping motor driver

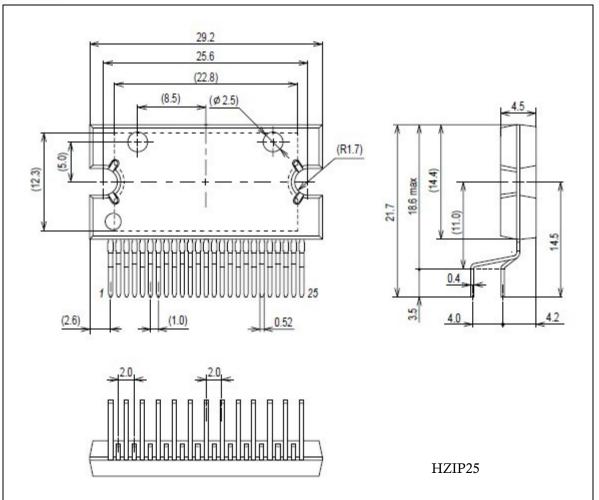

- 2. Package: HZIP25 (See attached case outline dimensions.)

- 3. Features

- 1 channel PWM current control stepping motor driver

- BiCDMOS process IC

- Output on-resistance (High side  $0.25 \Omega$ , Low side  $0.15 \Omega$ , Total  $0.40 \Omega$ ; Ta = 25°C, Io = 4.0 A)

- Selectable phase drive (1/2, 1/8, 1/16,1/32, 1/64, 1/128, 1/10, 1/20step)

- Advance the excitation step with the only step signal input

- Available forward reverse control

- Iomax=4.3A

- Over current protection circuit

- Thermal shutdown circuit

- Input pull down resistance

- With reset pin and enable pin

| Parameter             | Symbol  | Ratings     | Unit |

|-----------------------|---------|-------------|------|

| Supply voltage        | VMmax   | 50          | V    |

| Output current        | Iomax   | 4.3         | А    |

| Logic input voltage   | VINmax  | 6           | V    |

| VREF input voltage    | VREFmax | 6           | V    |

| MO input voltage      | VMOmax  | 6           | V    |

| DOWN input voltage    | VDOmax  | 6           | V    |

| Operating temperature | Topg    | -30 to +85  | °C   |

| Storage temperature   | Tstg    | -55 to +150 | °C   |

## 4. Absolute Maximum Ratings at $Ta = 25^{\circ}C$

5. Recommended Operating Range at Ta=25°C

| Parameter                 | Symbol | Ratings | Unit |

|---------------------------|--------|---------|------|

| Supply voltage range      | VM     | 9 to 45 | V    |

| Logic input voltage range | VIN    | 0 to 5  | V    |

| VREF input voltage range  | VREF   | 0 to 3  | V    |

| Parameter                   | Symbol  | Conditions                       | min  | typ  | max | Unit |

|-----------------------------|---------|----------------------------------|------|------|-----|------|

| Standby mode current drain  |         | ST="L"                           |      | 100  |     | μA   |

| current drain               | IM      | ST="H",OE="H", no load           |      | 4    |     | mA   |

| Thermal shutdown            | TSD     | Design guarantee                 | 150  | 180  | 210 | °C   |

| temperature                 |         |                                  |      |      |     |      |

| 5                           | ΔTSD    | Design guarantee                 |      | 40   |     | °C   |

| Logic pin input current     | IinL1   | VIN=0.8V                         |      | 8    |     | μA   |

|                             | IinH1   | VIN=5V                           |      | 50   |     | μA   |

| Logic input high-level      | Vinh    |                                  | 2.0  |      |     | V    |

| voltage                     |         |                                  |      |      |     |      |

| Logic input low-level       | Vinl    |                                  |      |      | 0.8 | V    |

| voltage                     |         |                                  |      |      |     |      |

| FDT pin high-level voltage  |         |                                  | 3.5  |      |     | V    |

| FDT pin middle-level        | Vfdtm   |                                  | 1.1  |      | 3.1 | V    |

| voltage                     |         |                                  |      |      |     |      |

| FDT pin low-level voltage   | Vfdtl   |                                  |      |      | 0.8 | V    |

| Chopping frequency          | Fch     | Cosc1=100pF                      |      | 100  |     | KHz  |

| OSC1 pin charge/discharge   | Iosc1   |                                  |      | 10   |     | μA   |

| current                     |         |                                  |      |      |     |      |

| Chopping oscillator circuit | Vtup1   |                                  |      | 1    |     | V    |

| threshold voltage           | Vtdown1 |                                  |      | 0.5  |     | V    |

| VREF pin input voltage      | Iref    | VREF=1.5V                        | -0.5 |      |     | μA   |

| DOWN output residual        | VolDO   | Idown=1mA                        |      |      | 400 | mV   |

| voltage                     |         |                                  |      |      |     |      |

| MO pin residual voltage     | VolMO   | Imo=1mA                          |      |      | 400 | mV   |

|                             | Falert  | Cosc2=1500pF                     |      | 1.6  |     | Hz   |

| frequency                   |         | 1                                |      |      |     |      |

| OSC2 pin charge/discharge   | Iosc2   |                                  |      | 10   |     | μA   |

| current                     |         |                                  |      |      |     | •    |

| Hold current switching      | Vtup2   |                                  |      | 1    |     | V    |

| frequency threshold voltage | Vtdown2 |                                  |      | 0.5  |     | V    |

| Blanking time               | Tbl     |                                  |      | 1    |     | uS   |

| Output block                |         |                                  | I    |      |     |      |

| *                           | Ronu    | Io=4.0A, high-side ON resistance |      | 0.25 |     | Ω    |

| 1                           | Rond    | Io=4.0A, low-side ON resistance  |      | 0.15 |     | Ω    |

| Output leakage current      | Ioleak  | VM=50V                           |      |      | 50  | μΑ   |

| Diode forward voltage       | VD      | ID=-4.0A                         |      | 1    |     | V    |

| Current setting reference   | VRF     | VREF=1.5V, Current ratio 100%    |      | 300  |     | mV   |

|                             |         |                                  |      | 200  |     | 1    |

## 6. Electrical Characteristics at Ta =25°C, VM=24V, VREF=1.5V

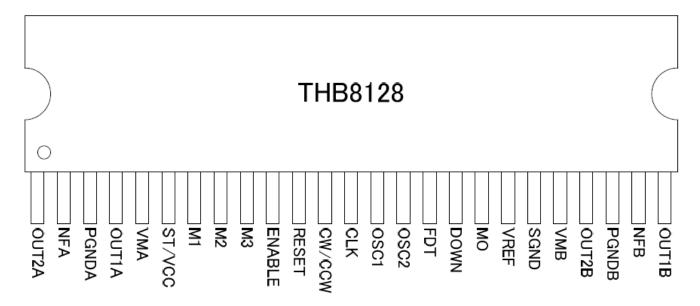

## 7. PIN ARRANGEMENT (Proposal)

## 8. Pin Functions

| Pin No. | Pin symbol | Pin Functions                                               |  |

|---------|------------|-------------------------------------------------------------|--|

| 17      | DOWN       | Holding current output                                      |  |

| 20      | SGND       | Signal GND                                                  |  |

| 14      | OSC1       | Chopping frequency setting capacitor connection             |  |

| 16      | FDT        | Decay mode select voltage input                             |  |

| 19      | VREF       | Constant-current control reference voltage input            |  |

| 21      | VMB        | B phase motor supply connection                             |  |

| 7       | M1         | Excitation-mode switching pin                               |  |

| 8       | M2         | Excitation-mode switching pin                               |  |

| 9       | M3         | Excitation-mode switching pin                               |  |

| 22      | OUT2B      | B phase OUTB output                                         |  |

| 24      | NFB        | B phase current sense resistance connection                 |  |

| 25      | OUT1B      | B phase OUTA output                                         |  |

| 23      | PGNDB      | B phase power GND                                           |  |

| 1       | OUT2A      | A phase OUTB output                                         |  |

| 2       | NFA        | A phase current sense resistance connection                 |  |

| 4       | OUT1A      | A phase OUTA output                                         |  |

| 3       | PGNDA      | A phase power GND                                           |  |

| 10      | ENABLE     | Output enable signal input                                  |  |

| 11      | RESET      | RESET signal input                                          |  |

| 5       | VMA        | A phase motor supply connection                             |  |

| 13      | CLK        | Clock pulse signal input                                    |  |

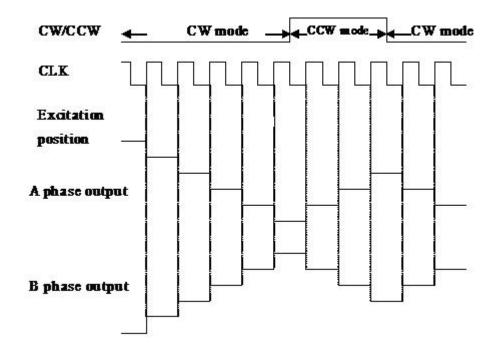

| 12      | CW/CCW     | Forward/Reverse signal input                                |  |

| 15      | OSC2       | Holding current detection time setting capacitor connection |  |

| 18      | МО         | Position detecting monitor                                  |  |

| 6       | ST/VCC     | Chip enable input                                           |  |

- 9. Description of functions

- 9-1) Stand-by function

When ST/VCC pin is at low levels, the IC enters stand-by mode, all logic is reset and output is turned OFF. When ST/VCC pin is at high levels, the stand-by mode is released.

9-2) Step pin function

CLK pin step signal input allows advancing excitation step.

| Input  |     | Operation            |

|--------|-----|----------------------|

| ST/VCC | CLK |                      |

| L      | *   | Stand-by mode        |

| Н      |     | Excitation step feed |

| Н      |     | Excitation step hold |

## 9-3) Excitation setting method

Set the excitation setting as shown in the following table by setting M1 pin, M2 pin and M3 pin.

| Input |    | Mode | Initial position |                 |                 |

|-------|----|------|------------------|-----------------|-----------------|

| M3    | M2 | M1   | (Excitation)     | A phase current | B phase current |

| L     | L  | L    | 1/2              | 100%            | 0%              |

| L     | L  | Н    | 1/8              | 100%            | 0%              |

| L     | Н  | L    | 1/16             | 100%            | 0%              |

| L     | Н  | Н    | 1/32             | 100%            | 0%              |

| Н     | L  | L    | 1/64             | 100%            | 0%              |

| Н     | L  | Н    | 1/128            | 100%            | 0%              |

| Н     | Н  | L    | 1/10             | 100%            | 0%              |

| Н     | Н  | Н    | 1/20             | 100%            | 0%              |

The initial position is also the default state at start-up and excitation position at counter-reset in each excitation mode.

## 9-4) Output current setting

Output current is set as shown below by the VREF pin (applied voltage) and a resistance value between NFA (B) pin and GND.

Iout = (VREF / 5) / NFA (B) resistance

\*\* The setting value above is a 100% output current in each excitation mode.

(Example) When VREF=1.5V and NFA (B) resistance is 0.3  $\Omega$ , the setting current is shown below. Iout = (1.5 V / 5) / 0.3  $\Omega$  = 1.0 A

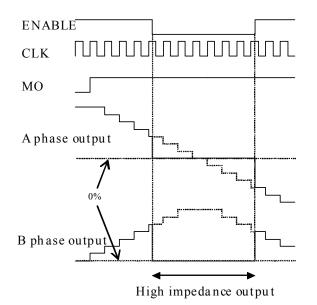

## 9-5) Output enable function

When the ENABLE pin is set Low, the output is forced OFF and goes to high impedance. However, the internal logic circuits are operating, so the excitation position proceeds when the CLK is input. Therefore, when ENABLE pin is returned to High, the output level conforms to the excitation position proceeded by the CLK input.

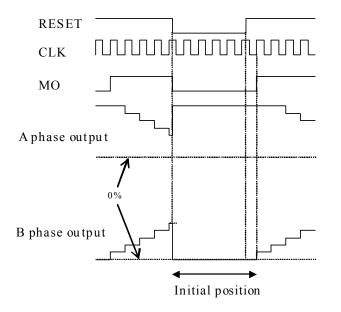

#### 9-6) Reset function

When the RESET pin is set Low, the output goes to initial mode and the excitation position is fixed in the initial position for CLK pin and CW/CCW pin input. MO pin outputs at low levels at the initial position. (Open drain connection)

9-7) Forward/reverse switching function

| CW/CCW | Operation |

|--------|-----------|

| L      | CW        |

| Н      | CCW       |

The internal D/A converter proceeds by a bit on the rising edge of the step signal input to the CLK pin. In addition, CW and CCW mode are switched by CW and CCW pin setting.

In CW mode, the B phase current is delayed by 90° relative to the A phase current. In CCW mode, the B phase current is advanced by 90° relative to the A phase current.

#### 9-8) DECAY mode setting

Current DECAY method is selectable as shown below by applied voltage to the FDT pin.

| FDT voltage  | DECAY method |

|--------------|--------------|

| 3.5V to      | SLOW DECAY   |

| 1.1V to 3.1V |              |

| or OPEN      | MIXED DECAY  |

| to 0.8V      | FAST DECAY   |

## 9-9) DOWN, MO output pin

Output pin is an open drain connection. Each pin is turned ON at predetermined state and outputs at low levels.

| Pin state | DOWN          | MO               |

|-----------|---------------|------------------|

|           | Holding       |                  |

| Low       | current state | Initial position |

|           |               | Non initial      |

| OFF       | Normal state  | position         |

## 9-10) Chopping frequency setting function

Chopping frequency is set as shown below by a capacitor between OSC1 pin and GND.

$Fcp = 1 / (Cosc1 / 10 \times 10^{-6}) (Hz)$

(Example) When Cosc1=100pF, the chopping frequency is shown below.

Fcp = 1 /  $(100 \times 10^{-12} / 10 \times 10^{-6}) = 100 \text{ (kHz)}$

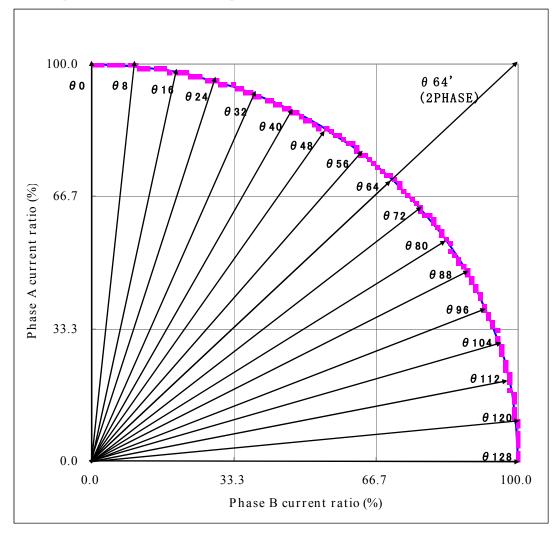

9-11) Output current vector locus (1 step normalized 90°)

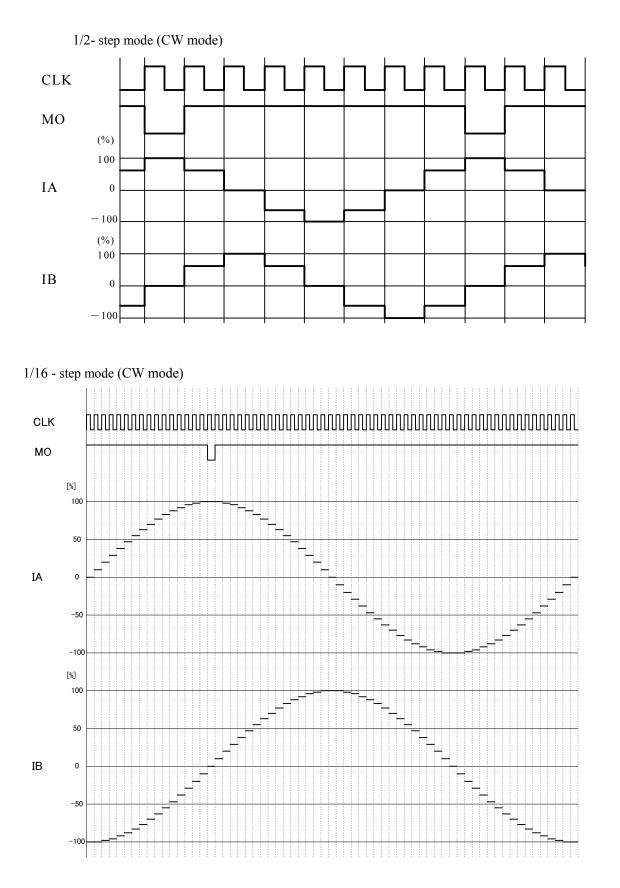

## 9-12) Current wave example in each excitation mode (1/2, 1/16 step mode)

#### 9-13) Output short-circuit protection circuit

Build-in output short-circuit protection circuit makes output to enter in stand-by mode. This function prevents the IC from damaging when the output shorts circuit by a voltage short or a ground short, etc. When output short state is detected, short-circuit detection circuit starts the operating and output is once turned OFF. After the timer latch time (typ: 256us), output is turned ON again. Still the output is at short state, the output is turned OFF and fixed in stand-by mode.

When output is fixed in stand-by mode by output short protection circuit, output is released the latch by setting ST/VCC="L".

9-14) Open-drain pin for switching holding current

The output pin is an open drain connection.

This pin is turned ON when no rising edge of CLK between the input signals while a period determined by a capacitor between OSC2 and GND, and outputs at low levels.

The open-drain output in once turned ON, is turned OFF at the next rising edge of CLK.

Holding current switching time (Tdown) is set as shown below by a capacitor between OSC2 pin and GND.

$Tdown = Cosc2 \times 0.4 \times 10^9 (s)$

(Example) When Cosc2=1500pF, the holding current switching time is shown below.

Tdown = 1500 pF  $\times$  0.4 $\times$ 10<sup>9</sup> = 0.6 (s)

## 10. Current control operation

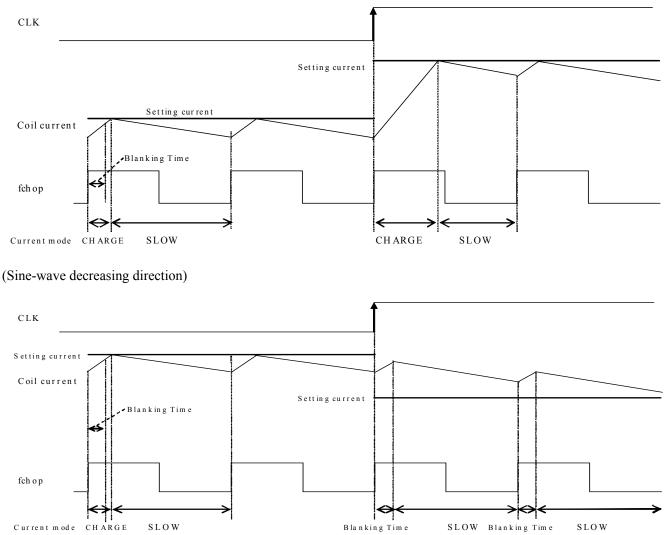

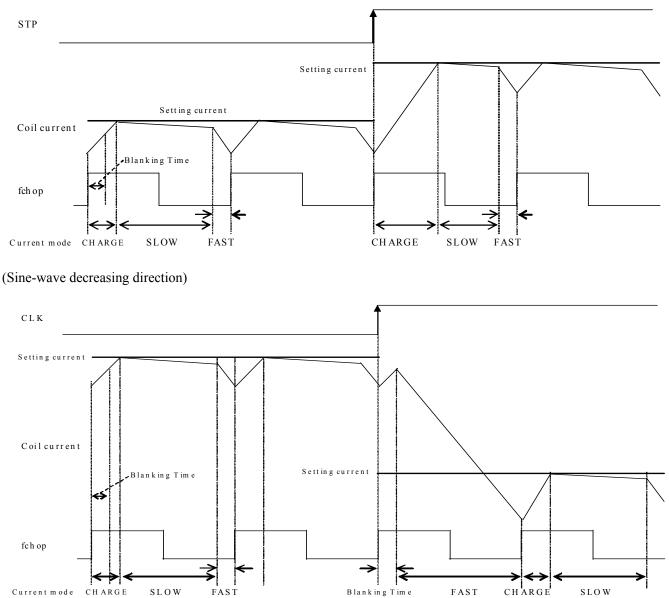

## 10-1) SLOW DECAY current control operation

When FDT pin voltage is a voltage over 3.5 V, the constant-current control is operated in SLOW DECAY mode.

(Sine-wave increasing direction)

Each of current modes operates with the follow sequence.

- The IC enters CHARGE mode at a rising edge of the chopping oscillation.

- (A period of CHARGE mode (Blanking Time) is forcibly present in approximately 1 µs, regardless of the current value of the coil current(ICOIL) and set current (IREF)).

- After the period of the blanking time, the IC operates in CHARGE mode until ICOIL > IREF. After that, the mode switches to the SLOW DECAY mode and the coil current is attenuated until the end of a chopping period.

- At the constant-current control in SLOW DECAY mode, following to the setting current from the coil current may take time (or not follow) for the current delay attenuation.

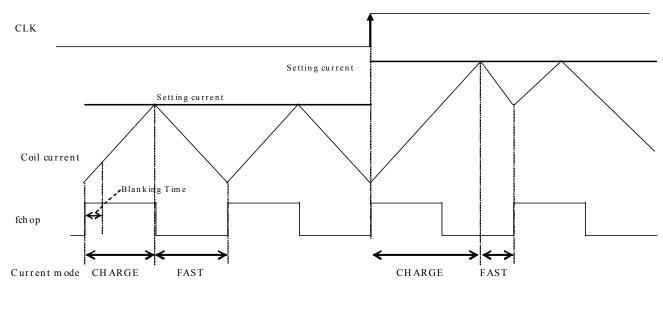

## 10-2) FAST DECAY current control operation

When FDT pin voltage is a voltage under 0.8V, the constant-current control is operated in FAST DECAY mode. (Sine-wave increasing direction)

## (Sine-wave decreasing direction)

Each of current modes operates with the follow sequence.

• The IC enters CHARGE mode at a rising edge of the chopping oscillation.

(A period of CHARGE mode (Blanking Time) is forcibly present in approximately 1 µs, regardless of the current value of the coil current (ICOIL) and set current (IREF)).

• After the period of the blanking time, The IC operates in CHARGE mode until ICOIL  $\geq$  IREF. After that, the mode switches to the FAST DECAY mode and the coil current is attenuated until the end of a chopping period.

At the constant-current control in FAST DECAY mode, following to the setting current from the coil current takes short-time for the current fast attenuation, but, the current ripple value may be higher.

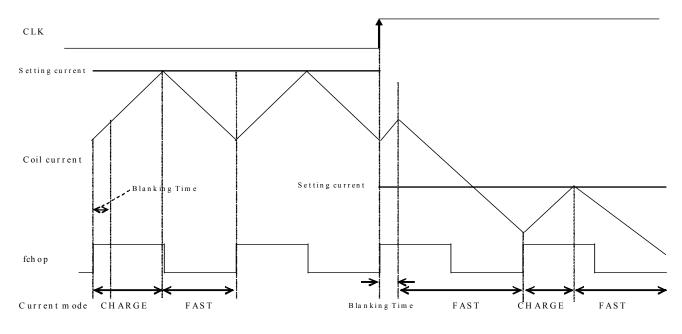

## 10-3) MIXED DECAY current control operation

When FDT pin voltage is a voltage between 1.1 V to 3.1 V or OPEN, the constant-current control is operated in MIXED DECAY mode. (Sine-wave increasing direction)

Each of current modes operates with the follow sequence.

• The IC enters CHARGE mode at a rising edge of the chopping oscillation.

(A period of CHARGE mode (Blanking Time) is forcibly present in approximately 1 µs, regardless of the current value of the coil current (ICOIL) and set current (IREF)).

• In a period of Blanking Time, the coil current (ICOIL) and the setting current (IREF) are compared.

If an ICOIL < IREF state exists during the charge period:

The IC operates in CHAGE mode until ICOIL  $\geq$  IREF. After that, it switches to SLOW DECAY mode and then switches to FAST DECAY mode in the last approximately 1 µs of the period.

If no ICOIL < IREF state exists during the charge period:

The IC switches to FAST DECAY mode and the coil current is attenuated with the FAST DECAY operation until the end of a chopping period.

The above operation is repeated.

Normally, in the sine wave increasing direction the IC operates in SLOW (+FAST) DECAY mode, and in the sine wave decreasing direction the IC operates in FAST DECAY mode until the current is attenuated and reaches the set value and the IC operates in SLOW (+FAST) DECAY mode.

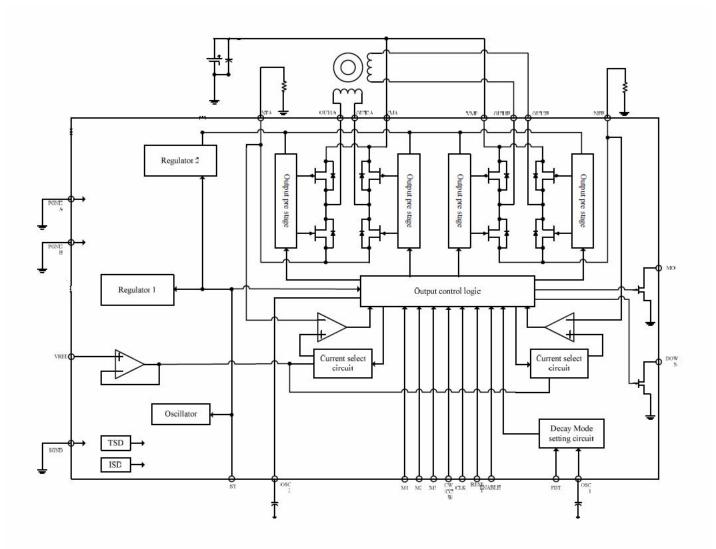

11. Block diagram

## 12.Package Dimensions

# unit : mm (typ) 3236A