# Sensorless Motor Drive with the ST62 MCU + TRIAC

T. CASTAGNET

### INTRODUCTION

Home appliance applications are requiring more and more electronic control in order to meet new requests and constraints of consumers.

Microcontrollers have been typically limited to high end applications because their performance appears to be overrated when related to the functions of the application. In reality, home appliances require microcontrollers which trade closely between the compromise between cost and performance.

An a.c. universal motor is a cost optimized solution for home appliance applications including food processor and drill applications.

This Application Note shows that the capabilities of simple 8-bit microcontroller allows the design of cost effective speed drive controller with increased functionality. When associated to a triac these microcontrollers become key components in the design of a sensorless speed control.

## **1 THE CONTROL OF THE MOTOR SPEED**

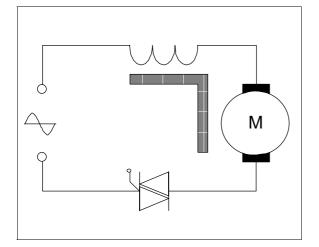

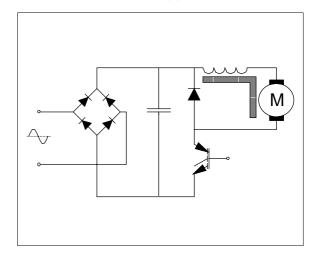

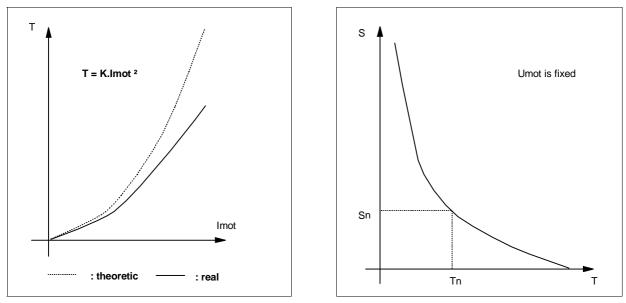

An a.c. universal motor is a brush motor with a serial excitation. Its stator windings are connected in series with the rotor, and its flux is proportional to the motor current. The motor torque is theoretically proportional to the square of the current, so it is always positive: the speed direction is insensitive to the current direction, and the motor can be supplied in a.c. or d.c. modes. Control of the speed is obtained by adjustment of the motor voltage. This control is achieved by a phase angle method in a.c. mode, or by a Pulse Width Modulation method in d.c. mode.

Figure 1. The triac is a key device for the a.c. drive of the universal motor.

Figure 2. A d.c. drive for the universal motor: the P.W.M. chopper with IGBT.

For a fixed motor voltage the motor characteristic shows that the motor speed changes when the torque is varied: the control of the speed requires feed-back of the speed itself.

Figure 3. Universal motor torque T versus the motor current Imot.

Figure 4. Universal motor characteristic speed torque (S,T) for a fixed motor voltage Umot.

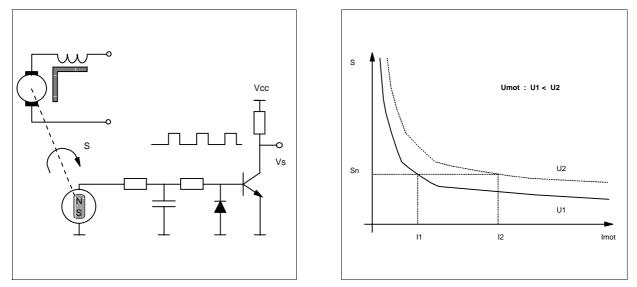

The tachogenerator is a classical speed sensor solution for home appliances. When the accuracy of the speed is not a critical parameter, speed control is also possible without any external speed sensors: thus reducing the number of components in the speed drive.

- SGS-THOMSON MICROELECTRONICS

*Figure 5. Speed measurement schematic based on tachogenerator sensor.*

Figure 6. Evaluation of the speed S versus current Imot & voltage Umot of the

The back electromotive force (b.e.m.f.) of the motor is a function of the speed and of the current. In the first approach it behaves as a resistance proportional to speed.

When the sensor is removed, the speed of the motor is determined by relating the average motor voltage and the average motor current. The controller defines the motor voltage by the triac triggering time (a.c. mode), or by the chopper duty cycle (d.c. mode). A shunt resistor allows the peak motor current to be sensed.

Such a control method is feasible despite potential motor saturation and the brush voltage. The relations are not linear, however a microcontroller can solve the relations by using look up tables for calculations.

To improve the behavior of the speed drive on dynamic operations, the controller can also consider the motor acceleration: this acceleration is represented by the motor current variation,  $\Delta I_{MOT}$ .

This control method can be applied to the home appliance applications when the requirement on the speed accuracy is not very high. The sensor is not required, so the cost of the drive is reduced and its reliability is improved.

## 2 AN APPLICATION EXAMPLE

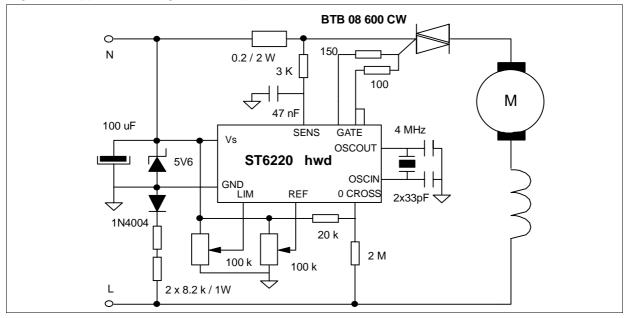

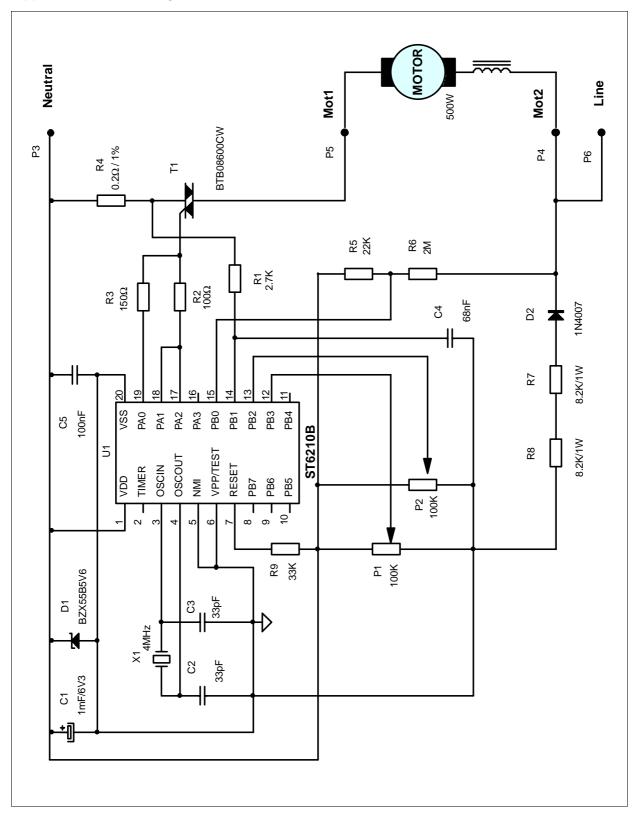

A basic speed drive has been designed with a 500 W a.c. universal motor. An 8 Amp - 600 V SNUBBERLESS triac drives the motor from the 230 V - 50 Hz mains. This drive is adapted to a drill application.

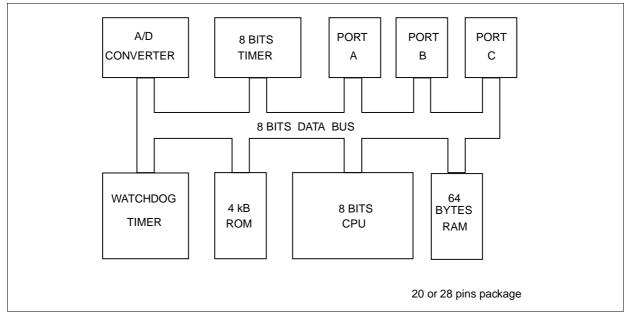

The speed drive control is fulfilled by an ST6220 microcontroller. This 8-bit microcontroller is able to calculate and to control the motor speed with no external sensor by using its on-chip analog/digital converter (A/D) for the current measurement and its 8-bit timer for the triac triggering control.

Figure 7. Application diagram of a speed drive for an 500 W a.c. universal motor.

A shunt resistor measures the peak motor current: it is connected in series with the triac, and is referred to the positive supply polarity. Two potentiometers define the speed reference and the torque limit. Two resistors allow the zero crossing of the line voltage to be captured.

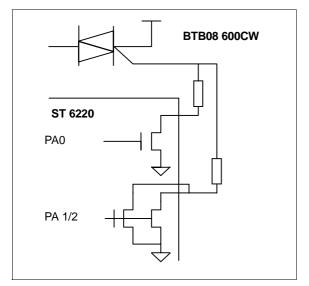

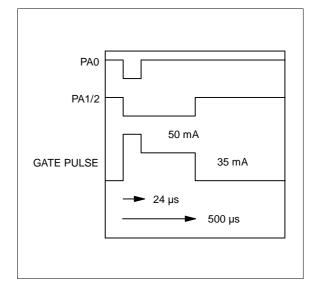

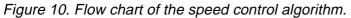

The microcontroller triggers the triac directly with its 20 mA outputs. At the triggering point three outputs supply a 50 mA gate current during 2 instruction cycles (24  $\mu$ s): this pulse will secure the triggering at low temperature or on accidental dl/dt. The two outputs then remain on during 500  $\mu$ s, supplying the gate triggering current (I<sub>GT</sub> = 35 mA) until the triac latches. The triac driver consumption then becomes less than 2 mA.

An auxiliary supply generates a voltage of 5.6V: the low consumption of the HCMOS microcontroller and the pulse mode triac triggering minimize the total consumption ( $I_{cc}$  < 5 mA). So the required current is supplied by two 8.2 k $\Omega$ /1W decoupling resistors.

*Figure 8a. Triac triggering with double pulse mode: diagram.*

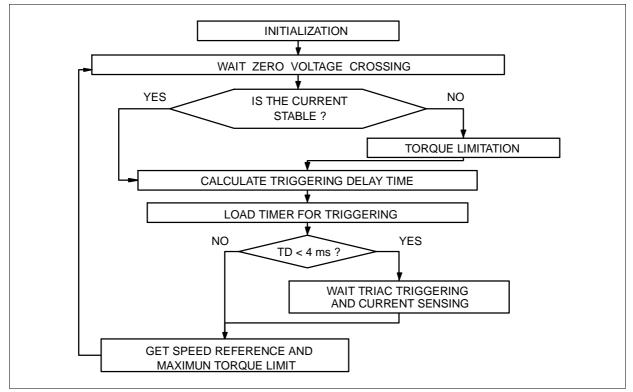

The control program achieves speed control and torque limitation. In addition to these functions, a current measurement task and a.c. phase control are also made by the software.

The speed control determines the motor voltage to be set and the triac triggering delay time  $T_D$ . At each mains cycle the A/D converter reads the value of the first potentiometer with a 64 step scale. This value defines the speed reference by the means of a 64 byte look up table. The controller compensates for the effect of the motor current on the speed: it determines the current correction through a 64 byte look up table.

Figure 8b. Triac triggering with double pulse mode: chronogram.

Finally it calculates the time  $T_D$  by a combination between the speed reference and the current correction.

The timer organizes the phase angle control. It is synchronized to the zero crossing of the mains voltage. It delays the triac triggering to  $T_D$  with an 0.5 % resolution and then generates the 500µs gate triggering pulse.

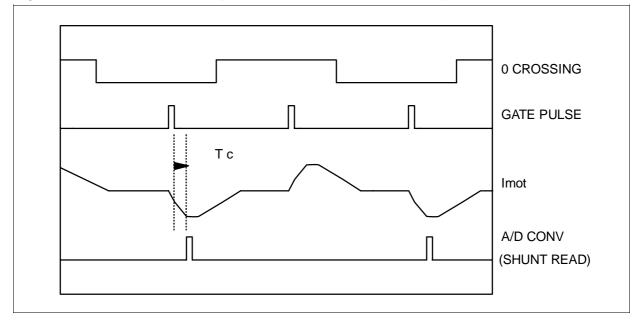

The motor current measurement is managed by software, saving the need for external peak detector components. After the triac is triggered, the timer synchronizes the A/D converter to read the shunt resistor. This read is done when the peak motor current is maximum. The peak current instant time  $T_c$  is determined versus the previous motor current value by the means of a 64 bytes look up table.

Figure 11. Flow chart of the 8 bits timer subroutine operation.

Figure 12. Measurement of the peak motor current with software peak detector.

The torque limitation controls the applied force of the drilling tool. The A/D converter reads the value of the second potentiometer to determine the requested torque limit on a 64 step scale. When the motor current is higher than this limit, the motor voltage is limited to a maximum value by limiting the delay time  $T_p$ .

The total controller program occupies 640 bytes of ROM Memory, including the look up tables of the speed reference, of the current correction, and of the current sense delay time.

This simple program is designed for one application. To change it for another application or motor, only the two look up tables related to the current (128 bytes) need to be modified. This microcontroller plus triac board can thus drive several motor types, or the performance of the board can be optimized for one or several fixed speeds. This flexibility is possible because of the MCU and of its 4 KByte memory size.

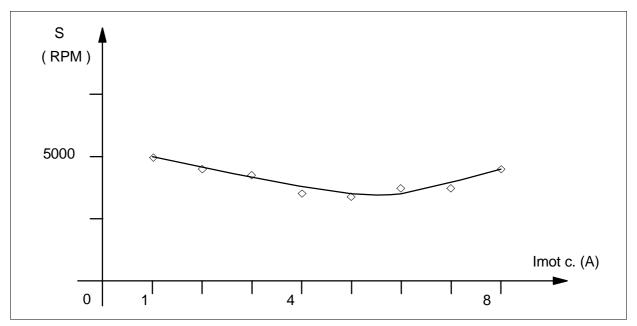

The speed of the designed drive ranges from 4000 to 25000 RPM. When the speed reference is 5000 RPM, the speed decreases down to 3500 RPM at 5A peak; it then increases up to 4500 RPM at 8A peak.

Figure 13. Variation of the speed S versus the peak motor current that represents the motor load.

The torque limitation is mainly effective at low speed: the torque can vary greatly and can decrease the quality of work of the tool. At high speed this limitation becomes useless because the torque and the current are naturally limited by the high impedance of the motor.

### **3 CONCLUSION**

This note presents a sensorless speed controller for an a.c. universal motor, using a SNUBBERLESS triac and an ST6220 microcontroller. The use of such a microcontroller permits the designer to reconsider the design of the brush motor speed drives: it also offers other methods to control the motor and simplifies the drive circuit by reducing the number of components used.

Moreover these ST62 microcontrollers increase the flexibility of the designed circuit. The same hardware circuit can fulfill the control of various motor types by changing only two look-up tables. Other functions such as the user interface (keyboard, display) can be easily added by software to the power control.

The same approach can be extended to motor control in D.C. mode where an IGBT/MOSFET chopper and microcontroller control by P.W.M. are designed.

This study has been made with the collaboration of the company B.F.E. (France), which has developped the program and the demonstration board.

#### **4 REFERENCES**

- [1] Power control with triacs and ST6210 MCU AN 392 - Ph. Rabier and L. Perier (SGS-THOMSON Microelectronics)

- [2] Digital control for brush DC motor

T. Castagnet and J. Nicolai (SGS-THOMSON Microelectronics) International Appliance Technics, May 93

- [3] Controlling a Brush DC motor with an ST6265

AN414 J. Nicolai and T. Castagnet (SGS-THOMSON Microelectronics) PCIM Nuremberg, June 93

- [4] Improved universal motor drives

J.M. Bourgeois, J.M. Charreton, and P. Rault (SGS-THOMSON Microelectronics)

AN422 Improved Universal Motor Drive with ST62

- [5] Improvement in the triac commutation AN 439 - P. Rault (SGS-THOMSON Microelectronics)

- [6] Data books of " SCRs and TRIACS" (DBSCRTRI/2) and " ST62XX MICROCONTROLLERS " (DBST6ST/3) (SGS-THOMSON Microelectronics)

**Appendix 1.** Sensorless speed control for the universal motor: customization of the control program.

The software of the motor control is provided in appendix 3 and is named sens01.asm. It can be adapted to an application by adjustment of the three look up tables (speed reference, peak current instant time, and current compensation).

During the adjustments of the speed range and of the peak current detection the current compensation should be inhibited by clearing the current correction register INDEX.

#### Adjustment of the no load speed range

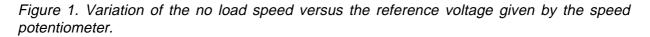

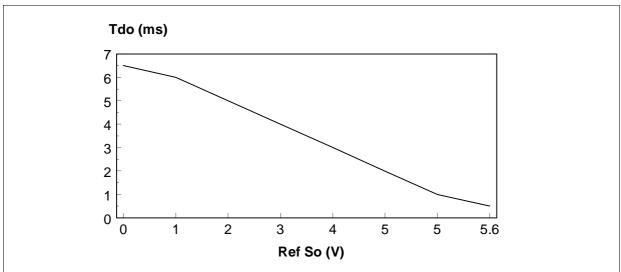

The potentiometer connected to PB2 (pin 13) defines the speed reference S in conjunction with a 64 byte look up table VITT. This reference corresponds to the motor voltage  $U_{MOT}$  and to the triggering delay time  $T_{D,O}$  at no load.

The table VITT contains all no load delay times  $T_{D_o}$  to define the speed range of the drive. The table values are defined by the full and minimum speed operation:

- the minimum triggering delay time (full speed) is defined by the motor power factor; the triac can only be triggered when its anode current is cancelled;

- the maximum triggering delay time (minimum speed) is chosen to keep sufficient motor magnetization, so as to maintain a relationship between motor torque and current.

The true decimal values of the tables are calculated by dividing the triggering delay time  $T_{D_{-}O}$  by the basic counting step of the timer (48 µs).

Figure 2. Variation of the no load triac triggering delay time vs the speed reference voltage.

## Adjustment of the peak current detection

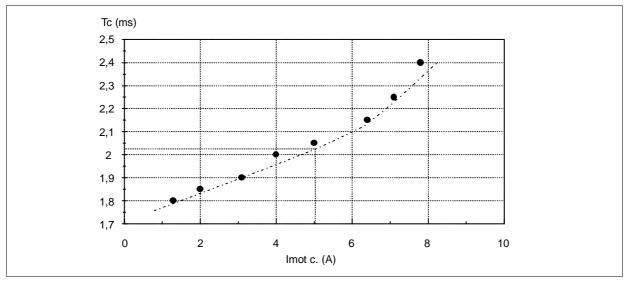

The peak current detection is made with the A/D converter connected on PB1 (pin 14). The timer synchronizes this operation to the triac triggering. The counted value is issued from a 64 byte look up table RTMES and it is defined versus the previous peak motor current  $I_{MOT C}$ . The table RTMES is optimized experimentally at the lowest speed  $S_{MIN}$ . The peak current instant  $T_c$  after triggering is registered by test for several current values which are chosen between 1 A (8d numeric) and 8 Apk (64d numeric). For each case the decimal table value is calculated by subtracting 650µs (triac triggering task duration) to the peak current instant  $T_c$ , and by dividing the result by the basic timer step (48 µs).

Figure 3. Experimental plotting of the peak current instant  $T_c$  versus the peak motor current  $I_{MOTC}$  at  $S_{MIN} = 5000$  RMP.

The other values of the table are calculated by linear interpolation on these 4 experimental points. The resulting table is fine tuned by a final test. The table is optimized for a speed  $S_{\text{MIN}}$ , but can extended to a larger speed range.

#### Adjustment of the current compensation

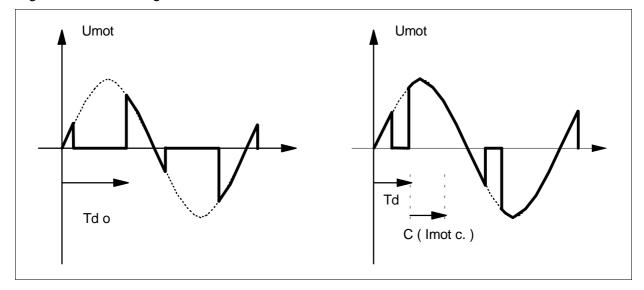

Figure 4. Motor voltage waveforms with no load and nominal load.

Speed control is done with a basic current compensation. When the load (and the motor current) increases, the controller has to increase the motor voltage: it increases the b.e.m.f. to maintain the motor speed.

The controller defines a current correction versus the peak motor current  $I_{MOT_{-C}}$ :  $C(I_{MOT_{-C}})$ . The triggering delay time  $T_{_{D}}$  is calculated by subtracting the no load triggering delay time  $T_{_{D_{-O}}}$  by this current correction:

$$T_{D_O} = T_D + C(I_{MOT_C})$$

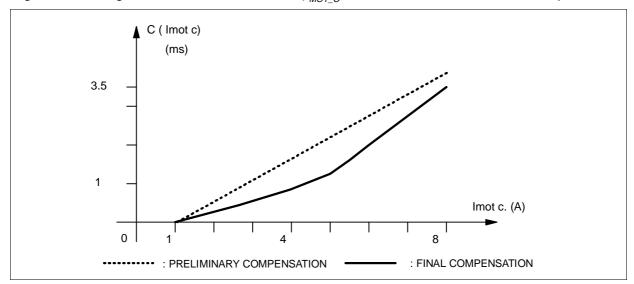

The current correction values are stored in the current compensation table COUPLE. This table is optimized for the lowest operational speed  $S_{MIN}$ , and its use could be applied to a larger speed range. The table calculation is done in two steps.

Figure 5. Plotting of the current correction  $C(I_{MOT})$  issued form the COUPLE look up table.

In the first step the current corrections  $C(I_{MOT_C})$  are determined experimentally to obtain a pure compensation of the current influence, and to maintain the speed round  $S_{MIN}$ . The INDEX register is loaded with an immediate value C, and the peak motor current is measured on test when the motor speed is at SMIN. The numeric current value defines directly the location of C in the table COUPLE. This test is done for several immediate INDEX values which are chosen between 0 and 80d (3.8 ms). The other values of the table are calculated by linear interpolation on these experimental points.

In the second step the effect of the preliminary defined compensation is reduced on lower motor current operation to give a good speed stability on dynamic operation. The current corrections which are decoded on lower motor current (less than 5 Apk), will be reduced and the resulting table will be tested on the speed drive. On the higher current range the corresponding corrections will be increased to maintain the speed in its operational range. The resulting table offers a non linear current compensation that gives a good compromise between the speed stability at lower current and the speed decreasing at higher current.

Appendix 2. Circuit diagram

#### Appendix 3. Software example program.

;\* ; \* SGS THOMSON MICROELECTRONICS ;\* ;\* SENSORLESS UNIVERSAL BRUSH MOTOR CONTROL ;\* VERSION 2.0 \* ;\* DECEMBER 1993 ;\* This program was developped with the partnership of the company \* ;\* \* B.F.E. . The address of our consultant is : ; \* Raymond PORTIER, B.F.E. 24, avenue du General LECLERC, 65200 Bagneres de Bigorre ;\* \* ;\* \* Tel : (33).62.91.03.00 Fax : (33).62.91.03.87 \* ;\* Circuit configuration and key features are : ;\* - ST6220 microcontroller is designed in \* ;\* \* - oscillator frequency : 4 MHz ;\* \* - hardware watchdog device is implemented ; \* - line zero crossing detection on PBO with interrupt ;\* - speed reference on PB2 ; torque limitation on PB3 ;\* \* - torque limitation is stopped ;\* - triac triggering delay time is between 0.4 and 6.5  $\ensuremath{\mathsf{ms}}$ ;\* - triac gate drive on PA1, PA2 with boost on PA0 ; \* - motor current detection on PB1 with ADC ;\* - current shunt is 0.2 Ohms and detectable peak current is less ;\* 8 Amps ;\* - motor current detection time is shown by PA3 pointer \* ;\* - soft start operation ;\* .W ON ;\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* REGISTER DECLARATION \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* Х .def 080h!M ; Index register. .def 081h .def 082h Υ ; Index register. V ; Short direct register. .def 083h W ; Short direct register. .def Offh!M ; Accumulator. А .def 0C0h PRA ; Port a data register. .def 0C1h PRB ; Port b data register. .def 0C4h ; Port a direction register. PRAD .def 0C5h ; Port b direction register. • PRBD .def 0CCh PRAO ; Port a option register. PRBO .def 0CDh ; Port b option register. .def 0C8h IOR ; Interrupt option register. DRWR .def 0C9h!M ; Data rom window register. .def 0D0h!M ADR ; A/D result register. .def 0D1h ; A/D control register. ADCR TPSC .def 0D2h ; Timer 1 prescaler register. .def 0D3h ; Timer 1 counter register. TCR ; Timer 1 status control register. .def 0D4h TSCR .def 0D8h WDR ; Watchdog register.

| ;******                                               | ****                                                                                                                             | DATA RAM REGISTERS ************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VALR<br>LOOP<br>DX<br>DY<br>DXb<br>DYb<br>FLIT        | .def 099h!M<br>.def 087h<br>.def 088h<br>.def 089h<br>.def 08Ah<br>.def 08bh<br>.def 08ch                                        | <pre>; motor current register<br/>; counter<br/>; back up of X<br/>; back up of Y<br/>; back up of Y<br/>; back up of Y<br/>; back up of Y<br/>; motor control flag register<br/>; b0 indicates 0 crossing pulse<br/>; b0 indicates 0 crossing pulse<br/>; b2 indicates timer operation on<br/>; triac triggering<br/>; b3 indicates line polarity versus Vdd<br/>; b4 indicates timer operation on<br/>; current sensing delay<br/>; b7 indicates timer operation<br/>; b1, b5, b6 are unused here</pre> |  |  |  |

| INDEX<br>ADCcou<br>ADCcoul<br>ADCvit<br>ADCvit1<br>DA | .def 08eh<br>.def 08dh<br>.def 08fh<br>.def 091h<br>.def 092h<br>.def 093h<br>.def 094h!M<br>.def 095h<br>.def 096h<br>.def 097h | <pre>; bi, bs, bo are unused here ; previous VALR register value ; soft start counter ; back up of port B data register ; motor current compensation register ; torque limitation register ; speed reference register ; back up of A ; back up of A</pre>                                                                                                                                                                                                                                                 |  |  |  |

|                                                       |                                                                                                                                  | EQUATE DEFINITION ************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| OFSET                                                 | .equ 008h                                                                                                                        | ; offset subtracted from motor current                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| OFSET1                                                | .equ 007h                                                                                                                        | ; in current compensation calculation<br>; offset subtracted from motor current                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| TGATE<br>TDTIM<br>TDMIN<br>TDMAX<br>START             | .equ 008h<br>.equ 053h<br>.equ 008h<br>.equ 09ch<br>.equ 002h                                                                    | <pre>; in measure delay time calculation<br/>; triac gate pulse duration 08h=385us<br/>; time limit to define priority between<br/>; timer &amp; potentiometers subroutines<br/>; minimum trig. delay time 08h=385us<br/>; maximum trig. delay time 9ch=9.0 ms<br/>; step of soft start operation</pre>                                                                                                                                                                                                   |  |  |  |

|                                                       | -                                                                                                                                | NNING OF PROGRAM AREA **********************************                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| .org 0800h<br>;***********************************    |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| VITT                                                  | .BYTE 76H,74h,<br>BYTE 66H,64h,<br>BYTE 58h,57H,<br>BYTE 4fH,4dH,<br>BYTE 3fH,3dH,<br>BYTE 2fH,2dH,                              | 22H,80H,7eH,7cH,7aH,78H<br>22H,70H,6eH,6cH,6aH,68H<br>52H,60H,5eH,5cH,5aH,59H<br>56H,55H,54H,53H,52H,51H<br>5DH,49H,47H,45H,43H,41H<br>5DH,39H,37H,35H,33H,31H<br>2DH,29H,27H,25H,23H,21H<br>5DH,19H,17H,15H,13H,11H                                                                                                                                                                                                                                                                                      |  |  |  |

| ;*************************************                |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| COUPLE                                                | .BYTE 06H,07H,<br>.BYTE 0cH,0dH,                                                                                                 | 1h,02H,03H,04H,04H,05H<br>7H,08H,09H,0ah,0aH,0bH<br>dh,0eH,0fH,10H,10H,11H<br>3H,14H,15H,16H,16H,17H                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 16/22                                                 |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

\_

|                           | .BYTE<br>.BYTE<br>.BYTE<br>.BYTE                                     | 18H,19H,19h,1aH,<br>1fH,20H,21H,22H,<br>27H,29H,2ah,2bH,<br>31H,33h,34H,35H,                                                                                 | 23н,24н,25н,26н<br>2сн,2ен,2fн,30н                                                                              |  |  |  |

|---------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| ;*                        |                                                                      | PEAK CURRENT II                                                                                                                                              | **************************************                                                                          |  |  |  |

| RTMES                     | .BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE<br>.BYTE | 0aH,0ah,10H,10H,<br>12H,12H,12H,13H,<br>14H,14H,14H,15H,<br>16H,16H,16H,16H,<br>17H,17H,17H,18H,<br>18H,19H,19H,19H,<br>1aH,1aH,1bH,1bh,<br>1dH,1dH,1eH,1eH, | 13H,13H,14H,14H<br>15H,15H,15H,15H<br>16H,17H,17H,17H•<br>18H,18H,18H,18H<br>19h,19H,1aH,1aH<br>1bH,1cH,1cH,1cH |  |  |  |

| ;*                        |                                                                      | INIT                                                                                                                                                         | **************************************                                                                          |  |  |  |

| start                     | ldi                                                                  | WDR,0feh                                                                                                                                                     | ; watchdog initialization                                                                                       |  |  |  |

| raz                       | ldi<br>clr<br>ld<br>inc<br>ld<br>cpi<br>jrc                          | x,084h<br>A<br>(X),A<br>X<br>A,X<br>A,0d5h<br>raz                                                                                                            | ; clear the RAM                                                                                                 |  |  |  |

| INIT                      | ldi<br>ldi<br>ldi                                                    | PRA, Ofh<br>PRAD, Ofh<br>PRAO, Ofh                                                                                                                           | ; port A in push pull output<br>; connected at Vdd                                                              |  |  |  |

|                           | ldi<br>ldi<br>ldi                                                    | PRB, 0eh<br>PRBD, 00h<br>PRBO, 03h                                                                                                                           | ; PB0 in interrupt input, PB1 in analog<br>; input, PB4/5/6/7 in pull up inputs,<br>; PB2/3 in HI input         |  |  |  |

|                           | ldi<br>ldi                                                           | ADR,00h<br>ADCR,00h                                                                                                                                          | ; A/D conv. initialization<br>; ADC is stopped                                                                  |  |  |  |

| ;                         | ldi<br>ldi<br>ldi<br>ldi<br>ldi<br>ldi                               | FLIT, 00h<br>COMPT, 0ah<br>INDEX, 00h<br>VALR, 00h<br>DVALR, 00h<br>ADCvit, 09fh                                                                             | ; clear logic and application registers<br>;<br>;<br>;<br>;<br>;                                                |  |  |  |

|                           | ldi                                                                  | IOR,10h                                                                                                                                                      | ; interrupt validation<br>; PB0 interrupt on falling edge                                                       |  |  |  |

| ;*****                    | reti<br>********                                                     | * * * * * * * * * * * * * * * * * * * *                                                                                                                      | *****                                                                                                           |  |  |  |

| ,<br>; *<br>; * * * * * * |                                                                      |                                                                                                                                                              |                                                                                                                 |  |  |  |

| ;*****                    | ******                                                               | ********* SOFT S                                                                                                                                             | TART TASK ************************************                                                                  |  |  |  |

| SOFT1                     | jrr<br>res<br>call<br>ldi                                            | 0,FLIT,SOFT1<br>0,FLIT<br>VIT<br>A,TDMAX                                                                                                                     | ; wait 0 crossing ( # 1 )                                                                                       |  |  |  |

| ;                         | ld                                                                   | A, ADCvit                                                                                                                                                    | ; ENABLE THIS INSTRUCTION TO INHIBIT                                                                            |  |  |  |

|                           |                                                                      |                                                                                                                                                              | SGS-THOMSON17                                                                                                   |  |  |  |

SGS-THOMSON MICROELECTRONICS

| SOFT2<br>ATINI<br>SOFT3<br>SOFT4    | jrr<br>res<br>ld<br>ldi<br>set<br>jrs<br>subi<br>cp<br>jrnc<br>jp<br>jp<br>ld | 0,FLIT,SOFT2<br>0,FLIT<br>TCR,A<br>TSCR,01111100b<br>7,FLIT<br>7,FLIT,ATINI<br>A, START<br>A, ADCvit<br>SOFT3<br>SOFT4<br>SOFT2<br>A, ADCvit | ;;;;;; | THE SOFT START<br>wait 0 crossing ( # 2,, n-1 )<br>reset b0 of FLIT<br>load timer register<br>start timer with interrupt & PSC = 16<br>control timer cycle with b7 indicator<br>wait end of timer operation |  |  |

|-------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ;*****                              | * * * * * * * *                                                               | *** MAIN MOTOR CON                                                                                                                           | TR     | OL PROGRAM ************************************                                                                                                                                                             |  |  |

| MAIN                                | jrr<br>res                                                                    | 0,FLIT,MAIN<br>0,FLIT                                                                                                                        | ;      | wait 0 crossing ( # n )                                                                                                                                                                                     |  |  |

| MAIN1                               | ldi<br>ld<br>subi<br>jrnc<br>clr                                              | DRWR,COUPLE.W<br>A, VALR<br>A, OFSET<br>MAIN4<br>A                                                                                           | ;      | define motor current compensation<br>A <= VALR motor current measure<br>A <= VALR - OFSET ,                                                                                                                 |  |  |

| MAIN4                               | cpi<br>jrc                                                                    | A, 040h<br>MAIN3                                                                                                                             | ;      | check VALR to max. value                                                                                                                                                                                    |  |  |

|                                     | ldi                                                                           | A, 03fh                                                                                                                                      | ;      | limit VALR to its max. value                                                                                                                                                                                |  |  |

| MAIN3                               | addi<br>ld                                                                    | A, 040h<br>X, A                                                                                                                              | ;      | load VALR@ in X register                                                                                                                                                                                    |  |  |

| MAIN2                               | ld                                                                            | A, (X)                                                                                                                                       |        | calculate current compensation data                                                                                                                                                                         |  |  |

| ;                                   | ; ***** TORQUE LIMITATION TASK *****                                          |                                                                                                                                              |        |                                                                                                                                                                                                             |  |  |

|                                     | qt                                                                            | MAINC                                                                                                                                        | ;<br>; | ENABLE THIS INSTRUCTION TO STOP<br>TORQUE LIMITATION                                                                                                                                                        |  |  |

|                                     | cp<br>jrc                                                                     | A, ADCcou<br>MAINc                                                                                                                           | ;      |                                                                                                                                                                                                             |  |  |

|                                     | ld                                                                            |                                                                                                                                              | ;      | limit to the max. requested torque                                                                                                                                                                          |  |  |

| ; ******* SPEED CONTROL TASK ****** |                                                                               |                                                                                                                                              |        |                                                                                                                                                                                                             |  |  |

| MAINC                               | ld                                                                            | INDEX,A                                                                                                                                      |        |                                                                                                                                                                                                             |  |  |

| ;                                   | ldi                                                                           | INDEX,00h                                                                                                                                    |        | ENABLE THIS INSTRUCTION TO INHIBIT<br>CURRENT COMPENSATION                                                                                                                                                  |  |  |

| MAIN5a                              | ld<br>sub<br>jrnc                                                             | A, ADCvit<br>A, INDEX<br>MAIN5                                                                                                               |        | load speed reference<br>substrate current comp. to speed ref.                                                                                                                                               |  |  |

|                                     | ldi                                                                           | A, TDMIN                                                                                                                                     | ;      | limit trig. delay time to min. value                                                                                                                                                                        |  |  |

| i                                   |                                                                               | **** PHASE ANGLE                                                                                                                             | C      | ONTROL TASK ****                                                                                                                                                                                            |  |  |

| MAIN5                               | ld<br>ldi<br>set                                                              | TCR,A<br>TSCR,01111100b<br>7,FLIT                                                                                                            | ;      | load timer for triac triggering delay<br>start timer with interrupt & PSC = 16<br>b7 <= 1, b7 indicates timer operation                                                                                     |  |  |

| i                                   |                                                                               | ***** DELAY TI                                                                                                                               | ME     | CONTROL *****                                                                                                                                                                                               |  |  |

|                                     | cpi<br>jrc                                                                    | A, TDTIM<br>MAINm                                                                                                                            |        | if Tdelay > TDMIN,<br>then read references before triggering                                                                                                                                                |  |  |

SGS-THOMSON

| ;                                               | * * * * *                                          | * SPEED REFERENCE                                                                                                   | & TORQUE LIMIT TASK *****                                                                                            |     |  |

|-------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|--|

| ATfin                                           | jrr<br>call<br>jrs<br>JP                           | 3,FLIT,ATfin<br>VIT<br>7,FLIT,ATfin<br>MAIN                                                                         | <pre>; read potentiometer when Vac is &gt; 0 ; read speed ref. &amp; torque lim. ; wait end of timer operation</pre> |     |  |

| MAINm<br>FIN                                    | jrs<br>jrr<br>call<br>jp                           | 7,FLIT,MAINm<br>3,FLIT,FIN<br>VIT<br>MAIN                                                                           | ; wait end of timer operation<br>; read potentiometer when Vac is > 0<br>; read speed ref. & torque lim.             |     |  |

| I, TIN                                          | 75                                                 | MAIN                                                                                                                |                                                                                                                      |     |  |

| ;*                                              |                                                    | PROGRAM S                                                                                                           | **************************************                                                                               | *   |  |

| ;*****                                          | * * * * * * * *                                    | * CURRENT MEASURE                                                                                                   | MENT SUBROUTINE ************************************                                                                 | *   |  |

| ADC                                             | ldi<br>ldi<br>ldi                                  | PRB, Oeh<br>PRBD, OOh<br>PRBO, O3h                                                                                  | ; PB1 in A/D input                                                                                                   |     |  |

| ADC1                                            | ldi<br>jrr<br>ld<br>com                            | ADCR, 30h<br>6,ADCR,ADC1<br>A, ADR<br>A                                                                             | <pre>; start conversion ; wait end of conversion ; A &lt;= ADR ; complement A/D result to obtain</pre>               |     |  |

| ADC2                                            | ld<br>ret                                          | VALR, A                                                                                                             | ; current measure referred to Vss<br>; update motor current measure in VALR                                          |     |  |

| ;*****                                          | ** SPEED                                           | REFERENCE & TORQ                                                                                                    | UE LIMITATION MEASURE SUBROUTINE ******                                                                              | * * |  |

| ;                                               | * *                                                | **** SPEED REFERE                                                                                                   | NCE MEASUREMENT TASK ******                                                                                          |     |  |

| VIT<br>VITadc                                   | ldi<br>ldi<br>ldi<br>jrr<br>ld<br>ld<br>ldi<br>ldi | PRB, 0eh<br>PRBD, 00h<br>PRBO, 05h<br>ADCR, 30h<br>6,ADCR,VITadc<br>A, ADR<br>ADCvit, A<br>X, ADCvit<br>ADCvit1,00h | ; PB2 input connected on A/D converter<br>; A/D conversion start<br>; wait at end of conversion                      |     |  |

|                                                 | call<br>ldi<br>ld<br>addi<br>ld<br>ld<br>ld        | DIV4<br>DRWR,VITT.W                                                                                                 | ; convert measured value in<br>; triac triggering delay time                                                         |     |  |

| ; ***** TORQUE REFERENCE MEASUREMENT TASK ***** |                                                    |                                                                                                                     |                                                                                                                      |     |  |

| COU                                             | ldi<br>ldi<br>ldi                                  | PRB, Oeh<br>PRBD, OOh<br>PRBO, O9h                                                                                  | ; PB3 input connected on A/D converter                                                                               |     |  |

| COU1                                            | ldi<br>jrr<br>ld<br>ld<br>ldi<br>ldi<br>call       | ADCR, 30h<br>6,ADCR, COU1<br>A, ADR<br>ADCcou, A<br>X, ADCcou<br>ADCcoul,00h<br>DIV4                                | ; A/D conversion start<br>; wait at end of conversion                                                                |     |  |

|                                                 |                                                    |                                                                                                                     | SGS-THOMSON                                                                                                          | 19  |  |

|                                                                                   | ldi<br>ld<br>addi<br>ld<br>ld<br>ld                                  | DRWR,COUPLE.W<br>A, ADCcoul<br>A, 40h<br>X, A<br>A, (X)<br>ADCcou,A              | ; convert measured value in<br>; triac triggering delay time |  |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| FVIT;*****                                                                        | ldi<br>ldi<br>ret<br>*******                                         | PRB, 0eh<br>PRBO, 03h                                                            | 4 SUBROUTINE ************************************            |  |

| ,<br>DIV4                                                                         | ldi                                                                  | LOOP, 06h                                                                        |                                                              |  |

| DIV42                                                                             | ld<br>sla<br>ld<br>inc<br>ld<br>rlc<br>ld<br>dec<br>jrz<br>dec<br>jp | A, (x)<br>A<br>(X),A<br>X<br>A, (X)<br>A<br>(X),A<br>LOOP<br>DIV41<br>X<br>DIV42 |                                                              |  |

| DIV41                                                                             | ret                                                                  |                                                                                  |                                                              |  |

| ;*****                                                                            | *****                                                                |                                                                                  | 5 SAVING SUBROUTINE ************************************     |  |

| SR                                                                                | ld<br>ld<br>ld<br>ld<br>ret                                          | DA, A<br>A, X<br>DX, A<br>A, Y<br>DY, A                                          | ; A>DA<br>; X>A<br>; A>DX<br>; Y>A<br>; A>DY                 |  |

| ;*****                                                                            | *****                                                                | REGISTER CONTEXT                                                                 | T RESTORING SUBROUTINE ***********************               |  |

| RSTR                                                                              | ld<br>ld<br>ld<br>ld<br>ld<br>ret                                    | A, DX<br>X, A<br>A, DY<br>Y, A<br>A, DA                                          | ; DX>A<br>; A>X<br>; DY>A<br>; A>Y<br>; DA>A                 |  |

| ;*****                                                                            | *****                                                                | REGISTER CONTEXT                                                                 | 5 SAVING SUBROUTINE ************************************     |  |

| SRb0                                                                              | ld<br>ld<br>ld<br>ld<br>ld<br>ret                                    | DAb,A<br>A, X<br>DXb,A<br>A, Y<br>DYb,A                                          | ; A>DAb<br>; X>A<br>; A>DX<br>; Y>A<br>; A>DY                |  |

| ;************ REGISTER CONTEXT RESTORING SUBROUTINE ***************************** |                                                                      |                                                                                  |                                                              |  |

| RSTRb0                                                                            | ld<br>ld<br>ld<br>ld<br>ld<br>ret                                    | A, DXb<br>X, A<br>A, DYb<br>Y, A<br>A, DAb                                       | ; DX>A<br>; A>X<br>; DY>A<br>; A>Y<br>; DAb>A                |  |

| ;*****                                                                            | ******                                                               | **** TIMER INTER                                                                 | RUPT SUBROUTINE ************************************         |  |

| 20/22                                                                             |                                                                      |                                                                                  | SGS-THOMSON                                                  |  |

|                                                                                   |                                                                      |                                                                                  | -J / • WICROELECTRONICS                                      |  |

| ITIM                                                                              | ldi<br>call             | TSCR,00h<br>SR                        | ; stop the timer<br>; save context                                                                          |  |  |

|-----------------------------------------------------------------------------------|-------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                   | jrs<br>jrs              | 2,FLIT,ITIM1<br>4,FLIT,ITIM2          | ; 2nd interrupt ?<br>; 3rd interrupt ?                                                                      |  |  |

|                                                                                   | set<br>ldi<br>nop       | 2, FLIT<br>PRA, 00h                   | ; 1st interrupt ; b2 <= 1<br>; TRIGGER THE TRIAC WITH BOOST<br>:                                            |  |  |

|                                                                                   | ldi                     | PRA, 01h                              | ,<br>; REDUCE GATE CURRENT and wait at triac<br>; latching ( PA0 turns off )                                |  |  |

|                                                                                   | ldi<br>ldi<br>jp        | TCR, TGATE<br>TSCR, 01111100b<br>FTIM | ; load timer triac triggering<br>; start timer & PSC = 16                                                   |  |  |

| ITIM1                                                                             | res<br>ldi<br>set       | 2, FLIT<br>PRA, 07h<br>4, FLIT        | ; 2nd interrupt<br>; STOP THE TRIAC GATE PULSE : pA to Vdd<br>; prepare 3rd interrupt                       |  |  |

|                                                                                   | ldi<br>ld               | DRWR, RTMES.W<br>A, VALR              | ; current measure delay time                                                                                |  |  |

|                                                                                   | subi<br>jrnc<br>clr     |                                       | ; A <= VALR - OFSET1                                                                                        |  |  |

| ITIM3                                                                             | cpi<br>jrc              |                                       |                                                                                                             |  |  |

| ITIM4                                                                             | ldi<br>addi<br>ld<br>ld | A, 040h                               |                                                                                                             |  |  |

|                                                                                   | ld<br>ldi<br>jp         | TCR, A<br>TSCR,01111100b<br>FTIM      | ; load timer with maesure. delay time<br>; start timer & PSC = 16                                           |  |  |

| ITIM2                                                                             | res<br>jrs              | 4, FLIT<br>3,FLIT,FTIM1               | ; 3rd interrupt<br>; sense motor current when Vac < 0                                                       |  |  |

|                                                                                   | ldi<br>call<br>ldi      | ADC                                   | ; pointer for current measure test<br>; if negative, measure shunt voltage<br>; end of pointer ( optional ) |  |  |

| FTIM1                                                                             | res                     | 7, FLIT                               | ; END OF TIMER OPERATION                                                                                    |  |  |

| FTIM                                                                              | call<br>reti            | RSTR                                  | ; restore context                                                                                           |  |  |

| ;********************* 0 CROSSING INTERRUPT SUBROUTINE ************************** |                         |                                       |                                                                                                             |  |  |

| IPB                                                                               | ldi<br>call             | WDR, Ofeh<br>SRb0                     | ; watchdog control<br>; save context                                                                        |  |  |

|                                                                                   | jrr                     | 3,FLIT,IPB1                           | ; test on line half cycle polarity                                                                          |  |  |

|                                                                                   | res<br>ldi<br>jp        | 3, FLIT<br>IOR, 30h<br>IPB2           | ; negative half cycle operation<br>; prepare rising edge interrupt                                          |  |  |

| IPB1                                                                              | set<br>ldi              | 3, FLIT<br>IOR, 10h                   | ; positive half cycle operation<br>; prepare falling edge interrupt                                         |  |  |

| IPB2                                                                              | set<br>call<br>reti     | 0, FLIT<br>RSTRb0                     | ; 0 crossing indicator validation<br>; restore context                                                      |  |  |

| ;*************************************                                            |                         |                                       |                                                                                                             |  |  |

|                                                                                   |                         |                                       |                                                                                                             |  |  |

| IADC<br>IPA<br>IMNI | reti<br>reti<br>reti            |                                   |    |                                             |

|---------------------|---------------------------------|-----------------------------------|----|---------------------------------------------|

| ;*****              | ********<br>.org 0f             | ******** INTERRUP<br>f0h          | ΤV | ECTORS ************************************ |

|                     | jp<br>jp<br>jp<br>jp<br>.org Of | IADC<br>ITIM<br>IPB<br>IPA<br>fch | ;  | adc<br>timer<br>port b and c<br>port a      |

| ;*****              | qt<br>qt                        | IMNI<br>start<br>*********        | ;  |                                             |

THE SOFTWARE INCLUDED IN THIS NOTE IS FOR GUIDANCE ONLY. SGS-THOMSON SHALL NOT BE HELD LIABLE FOR ANY DIRECT, INDIRECT OR CONSEQUENTIAL DAMAGES WITH RESPECT TO ANY CLAIMS ARISING FROM USE OF THE SOFTWARE.

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

Purchase of I<sup>2</sup>C Components by SGS-THOMSON Microelectronics, conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in an I<sup>2</sup>C system, is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

SGS-THOMSON Microelectronics GROUP OF COMPANIES Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom -