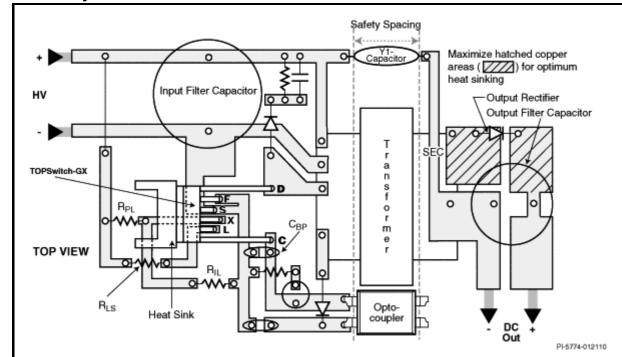

## **Board Layout Recommendations**

Click on the "Show me" icon to highlight relevant areas on the sample layout.

|   | Description                                                                                                               | Show Me |

|---|---------------------------------------------------------------------------------------------------------------------------|---------|

| 1 | Minimize loop area formed by drain, clamp and transformer                                                                 | ?       |

| 2 | Bias winding and bias capacitor are a power connection and therefore returned to Kelvin connection at SOURCE pin          |         |

| 3 | Any traces to the L or X pins should be kept as short as possible and away from the DRAIN trace to prevent noise coupling | ?       |

| 4 | Place line sense resistors RLS1 and RLS2 as close to the L pin as possible                                                | ?       |

| 5 | Minimize loop area formed by secondary winding, the output diode and the output filter capacitor                          | ?       |

2014.01.17. 12:44:04