# SONY CXK5814F

# 2048-word × 8 bit High Speed CMOS Static RAM

#### Description

The CXK5814P is a 16,384 bits high speed CMOS static RAM organized as 2,048 words  $\times$  8 bits and operates from a single 5V supply.

The CXK5814P is suitable for use in high speed and low power applications in which battery back up for nonvolatility is required.

#### **Features**

• Fast access time: 35 ns/45 ns/55 ns (Max.)

Low power standby: 5 μW (Typ.)—L-version 100 μW (Typ.)—Standard

version

· Low power operation: 300 mW (Typ.)

Single +5V supply

• Fully static memory . . . . No clock or timing strobe required

· Equal access and cycle time

. Common data input and output: three-state output

. Directly TTL compatible: All inputs and outputs

. Low voltage data retention: 2.0V (Min.)

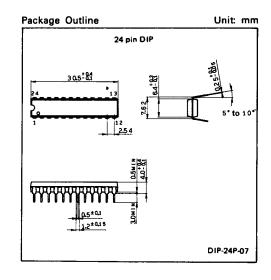

· High density: 300 mil 24 pin plastic package

#### **Function**

2048-word × 8 bit static RAM

#### Structure

Silicon Gate CMOS IC

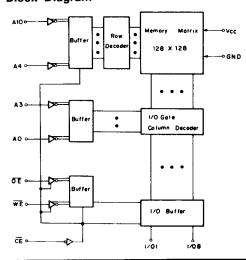

#### **Block Diagram**

#### Pin Configuration (Top View)

| Symbol       | Description         |

|--------------|---------------------|

|              |                     |

| A0 to A10    | Address Input       |

| I/01 to I/08 | Data Input Output   |

| CE           | Chip Enable Input   |

| WE           | Write Enable Input  |

| ŌĒ           | Output Enable Input |

| Vcc          | Power Supply        |

| GND          | Ground              |

# **Absolute Maximum Ratings**

| Item                        | Symbol            | Rating           | Unit        |

|-----------------------------|-------------------|------------------|-------------|

| Power Supply Voltage        | Vcc               | -0.5* to +7.0    | <b>&gt;</b> |

| Input Voltage               | Vin               | -0.5* to Vcc+0.5 | ٧           |

| Input and Output Voltage    | V <sub>I</sub> /O | -0.5* to Vcc+0.5 | ٧           |

| Allowable Power Dissipation | PD                | 1.0              | W           |

| Operating Temperature       | Topr              | 0 to +70         | °C          |

| Storage Temperature         | Tstg              | -55 to +150      | °C          |

| Soldering Temperature       | Tsolder           | 260 • 10         | °C • sec    |

<sup>\*</sup>  $V_{CC}$ ,  $V_{IN}$ ,  $V_{I/O}$  min=-3.5V for 20 ns pulse.

#### **Truth Table**

| ČE | ŌĒ | WE | Mode           | I/O 1 to I/O 8 | Vcc Current |

|----|----|----|----------------|----------------|-------------|

| H  | X  | х  | Not Selected   | High Z         | ISB1, ISB2  |

|    | Н  | Н  | Output Disable | High Z         | Icc1, Icc2  |

|    | L  | н  | Read           | Dout           | Icc1, Icc2  |

|    | ×  | L  | Write          | Din            | Icc1, Icc2  |

X: "H" or "L"

# **DC Recommended Operating Conditions**

(Ta=0 to +70°C, GND=0V)

|                      |        | ١,   |       |         |      |

|----------------------|--------|------|-------|---------|------|

| Item                 | Symbol | Min. | Typ.* | Max.    | Unit |

| Power Supply Voltage | Vcc    | 4.5  | 5.0   | 5.5     | ٧    |

| Input High Voltage   | ViH    | 2.2  | _     | Vcc+0.3 | ٧    |

| Input Low Voltage    | VIL    | -0.3 | _     | 0.8     | ٧    |

<sup>\*</sup> Vcc=5V, Ta=25°C

#### DC and Operating Characteristics

$(Vcc=5V\pm10\%, GND=0V, Ta=0 to +70^{\circ}C)$

|                        |                  |                                                                                                 |                     | 1.00 | 0 1             | 0,0, 0 | .,,, | , I a                    | 0 10 | . , , , |    |    |    |

|------------------------|------------------|-------------------------------------------------------------------------------------------------|---------------------|------|-----------------|--------|------|--------------------------|------|---------|----|----|----|

| Item                   | Symbol           | Symbol Test condition                                                                           |                     |      | XK581<br>35/45/ |        | 1    | CXK5814P<br>-35L/45L/55L |      |         |    |    |    |

|                        |                  |                                                                                                 |                     | Min. | Тур.            | Max.   | Min. | Тур.                     | Max. | 1       |    |    |    |

| Input Leakage Current  | lu               | VIN=GND to V                                                                                    | cc′                 | -2   | _               | 2      | -2   | -                        | 2    | μΑ      |    |    |    |

| Output Leakage Current | lto              | CE=VIH OF OE=VIH VI/O=GND to Vcc                                                                |                     | -2   | -               | 2      | -2   | _                        | 2    | μΑ      |    |    |    |

| Operating Power        |                  | CE=VIL                                                                                          | 35/35L              | _    | 60              | 85     | _    | 60                       | 85   | mA      |    |    |    |

| Supply Current         | Icc1 Iout=OmA    | Icc1                                                                                            | Icc1                | lcc1 |                 | 45/45L | _    | 50                       | 70   |         | 50 | 70 | mA |

|                        |                  | 55/55L                                                                                          |                     | 40   | 60              | _      | 40   | 60                       | mA   |         |    |    |    |

| Average Operating      |                  | Cycle=Min                                                                                       | 35/35L              | _    | 70              | 95     | -    | 70                       | 95   | mA      |    |    |    |

| Current                | Icc2             | Duty=100%                                                                                       | 45/45L              | _    | 60              | 80     | _    | 60                       | 80   | mA      |    |    |    |

|                        |                  | Iout=0mA                                                                                        | 55/55L              | _    | 50              | 70     |      | 50                       | 70   | mA      |    |    |    |

| Standby Current        | Is <sub>B1</sub> | CE≧V <sub>CC</sub> -0.2V,<br>V <sub>IN</sub> ≧V <sub>CC</sub> -0.2V or<br>V <sub>IN</sub> ≦0.2V |                     | _    | 0.02            | 1.0    |      | 0.001                    | 0.05 | mA      |    |    |    |

|                        | ISB2             | CE=VIH, VIN=V                                                                                   | CE=VIH, VIN=VIH/VIL |      | 15              | 25     | _    | 15                       | 25   | mA      |    |    |    |

| Output High Voltage    | Voн              | lон=−4.0 mA                                                                                     | lон=−4.0 mA         |      | _               | _      | 2.4  | _                        |      | V       |    |    |    |

| Output Low Voltage     | Vol              | lot=8.0 mA                                                                                      |                     | _    | _               | 0.4    | _    | _                        | 0.4  | V       |    |    |    |

#### Capacitance

(Ta=25°C, f=1 MHz)

| Item                     | Symbol | Test Condition       | Min. | Max. | Unit |

|--------------------------|--------|----------------------|------|------|------|

| Input Capacitance        | Cin    | VIN=0V               | _    | 5    | рF   |

| Input/Output Capacitance | Ci/o   | V <sub>1/0</sub> =0V | _    | 7    | рF   |

Note) This parameter is sampled and is not 100% tested.

## **AC Operating Characteristics**

#### . AC Test condition

(Vcc=5V±10%, Ta=0 to +70°C)

| Item                                       | Condition |  |  |  |  |

|--------------------------------------------|-----------|--|--|--|--|

| Input Pulse High Level                     | ViH=3.0V  |  |  |  |  |

| Input Pulse Low Level                      | VIL=0V    |  |  |  |  |

| Input Rise Time                            | tr=5 ns   |  |  |  |  |

| Input Fall Time                            | tr=5 ns   |  |  |  |  |

| Input and Output Timing<br>Reference Level | 1.5V      |  |  |  |  |

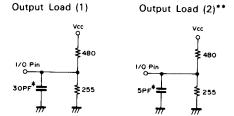

| Output Load                                | Fig. 1    |  |  |  |  |

\* including scope and jig

\*\* for tLZ, tHZ, tOHZ, tOLZ, tOW, tWHZ

Fig. 1

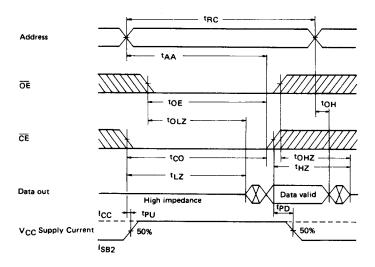

# Read Cycle

| ltem                                    | Symbol | CXK5814P<br>-35/35L |      | l    | 814P<br>'45L | CXK5 | Unit |    |

|-----------------------------------------|--------|---------------------|------|------|--------------|------|------|----|

|                                         |        | Min.                | Max. | Min. | Max.         | Min. | Max. |    |

| Read Cycle Time                         | trc    | 35                  | _    | 45   | _            | 55   | _    | ns |

| Address Access Time                     | taa    | _                   | 35   | _    | 45           | _    | 55   | ns |

| Chip Enable Access Time                 | tco    | _                   | 35   |      | 45           | _    | 55   | ns |

| Output Enable to Output Valid           | toE    | _                   | 20   | _    | 20           | _    | 25   | ns |

| Output Hold from<br>Address Change      | ton    | 5                   | _    | 5    | _            | 5    | _    | ns |

| Chip Enable to Output in Low Z (CE)     | tız*   | 5                   | _    | 5    | _            | 5    | _    | ns |

| Output Enable to Output in Low Z (OE)   | toLZ*  | 0                   | _    | 0    | _            | 0    |      | ns |

| Chip Disable to Output in High Z (CE)   | tHZ*   | 0                   | 20   | 0    | 20           | 0    | 20   | ns |

| Output Disable to Output in High Z (OE) | tonz*  | 0                   | 15   | 0    | 15           | 0    | 20   | ns |

| Chip Enable to Power<br>Up Time         | tPU    | 0                   | _    | 0    |              | 0    |      | ns |

| Chip Disable to Power<br>Down Time      | tPD    | _                   | 30   | _    | 30           |      | 30   | ns |

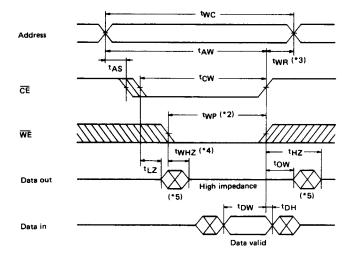

## Write Cycle

| ltem                               | Symbol | CXK5814P<br>-35/35L |      |      | 814P<br>/45L | CXK5<br>-55, | Unit |    |

|------------------------------------|--------|---------------------|------|------|--------------|--------------|------|----|

|                                    | ·      | Min.                | Max. | Min. | Max.         | Min.         | Max. |    |

| Write Cycle Time                   | twc    | 35                  |      | 45   | _            | 55           | _    | ns |

| Address Valid to End of Write      | taw    | 30                  |      | 40   |              | 50           | -    | ns |

| Chip Enable to End of Write        | tcw    | 30                  | _    | 40   |              | 50           |      | ns |

| Data to Write Time Overlap         | tow    | 15                  | _    | 20   | _            | 25           | _    | ns |

| Data Hold from Write Time          | tон    | 0                   | _    | 0    | _            | 0            | _    | ns |

| Write Pulse Width                  | twp    | 30                  | _    | 35   | -            | 40           | _    | ns |

| Address Setup Time                 | tas    | 0                   | _    | 0    |              | 0            | _    | ns |

| Write Recovery Time                | twn    | 0                   | _    | 0    | _            | 0            |      | ns |

| Output Active from<br>End of Write | tow*   | 5                   |      | 5    | _            | 5            | _    | ns |

| Write to Output in High Z          | tw+z*  | 0                   | 20   | 0    | 20           | 0            | 20   | ns |

<sup>\*</sup>Note) Transition is measured ±500 mV from steady state voltage with specified loading in Fig. 1. These parameters are sampled and not 100% tested.

#### **Timing Waveform**

# (1) Read Cycle [WE=VIH]

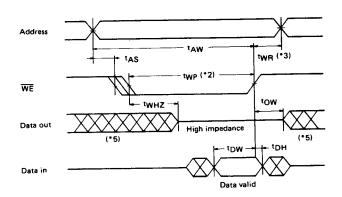

# (2) Write Cycle

• Write Cycle No.1: [OE=VIL or VIH] (\*1)

• Write Cycle No.2: [OE=VIL or VIH, CE=VIL] (\*1)

#### \* Notes)

- 1. If  $\widetilde{\text{OE}}$  is high, output remains in a high impedance state.

- 2. A write occurs during the low overlap of  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$ .

- 3. two is measured from the earlier of  $\overline{\overline{CE}}$  or  $\overline{WE}$  going high to the end of write cycle.

- 4. If  $\overline{\text{CE}}$  low transition occurs simultaneously with the  $\overline{\text{WE}}$  low transition or after the  $\overline{\text{WE}}$  transition, output remains in a high impedance state.

- 5. During this period, I/O pins are in the output state so that the input signals of opposite phase to the output must not be applied.

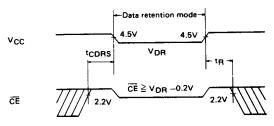

# **Data Retention Characteristics**

(Ta=0 to +70°C)

| Item                          | Symbol Test condition |                                     |          |      | KK581 |             | CXK5814P<br>-35L/45L/55L |             |             | Unit |

|-------------------------------|-----------------------|-------------------------------------|----------|------|-------|-------------|--------------------------|-------------|-------------|------|

|                               | Symbol                | , coc condition                     |          |      | Тур.  | Max.<br>5.5 | Min.<br>2.0              | Typ.<br>5.0 | Max.<br>5.5 |      |

| Data Retention Voltage VDR C  |                       | CE≧Vcc−0.2V                         | 2.0      | 5.0  | ٧     |             |                          |             |             |      |

|                               |                       | CE≧Vcc-0.2V                         | Vcc=3.0V |      | 12    | 600         |                          | 0.6         | 30          | μΑ   |

| Data Retention Current        |                       | Vin≦0.2V or                         | Vcc=2.0  |      | 20    | 1000        |                          | 1.0         | 50          | μΑ   |

| Data Retention<br>Set up Time | tcdrs                 | Chip disable to data retention mode |          | 0    |       |             | 0                        |             |             | ns   |

| Recovery Time                 | tR                    |                                     |          | trc* |       |             | trc*                     |             |             | ns   |

<sup>\*</sup>tRC: Read Cycle Time

#### **Data Retention Waveform**

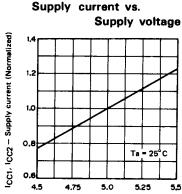

V<sub>CC</sub> - Supply voltage (V)

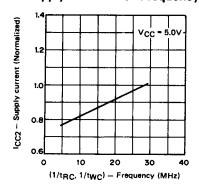

# Supply current vs. Frequency

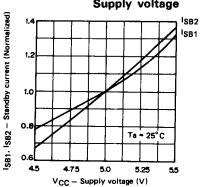

Standby current vs. Supply voltage

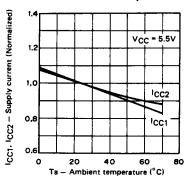

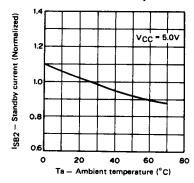

### Supply current vs. Ambient temperature

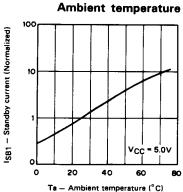

## Standby current vs. Ambient temperature

Standby current vs.

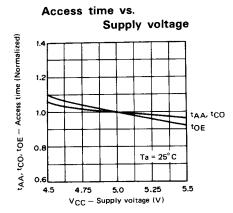

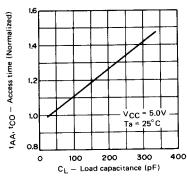

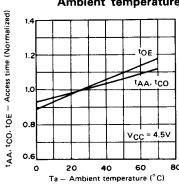

Access time vs.

Load capacitance

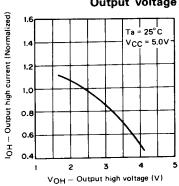

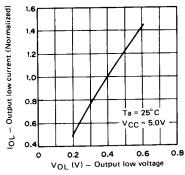

Output current vs.

Output voltage

Access time vs.

Ambient temperature

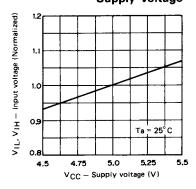

Input voltage vs.

Supply voltage

Output current vs.

Output voltage