# MOS INTEGRATED CIRCUIT $\mu$ PD16306A

#### 64-BIT HIGH-VOLTAGE CMOS DRIVER

The  $\mu$ PD16306A is a high-voltage CMOS driver for flat display panels such as FIPs and ELs. It consists of a 64-bit bidirectional shift register, a 64-bit latch, and a high-voltage CMOS driver. The logic operates on 5 V (CMOS level input) so that it can be directly connected to a microcomputer. The drivers can output a voltage as high as 80 V at 25 mAMAX. Because both the logic and drivers are created by CMOS process, they dissipate only a tiny amount of power.

#### **FEATURES**

- · 64-bit bidirectional shift driver

- · Data control through transfer lock (external) and latch

- High-speed data transfer (fmax. = 16 MHzmin., in cascade connection)

- Wide operating temperature range (T<sub>A</sub>. = -40 to 85 °C)

- High-voltage output (80 V, 25 mAмах.)

- · High-voltage CMOS process

- · Polarities of all drivers can be reversed by using PC pin.

#### ORDERING INFORMATION

| Part Number     | Package                                                |

|-----------------|--------------------------------------------------------|

| μPD16306AGF-3BA | 100-pin plastic QFP<br>(Iron lead frame: PD = 1.0 W)   |

| μPD16306AGF-3RA | 100-pin plastic QFP<br>(Copper lead frame: PD = 1.3 W) |

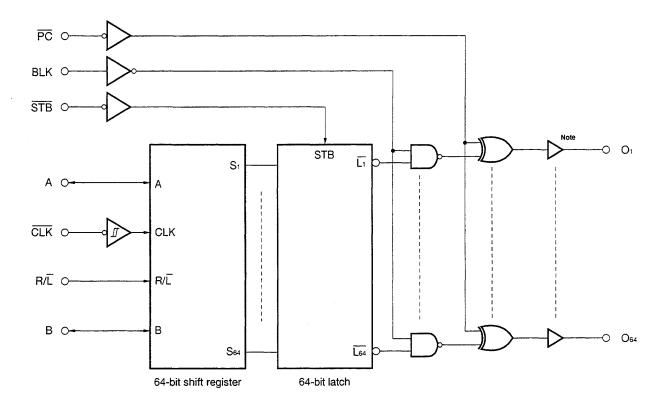

# **BLOCK DIAGRAM**

Note High-voltage CMOS drivers (80 V ±25 mAmax.)

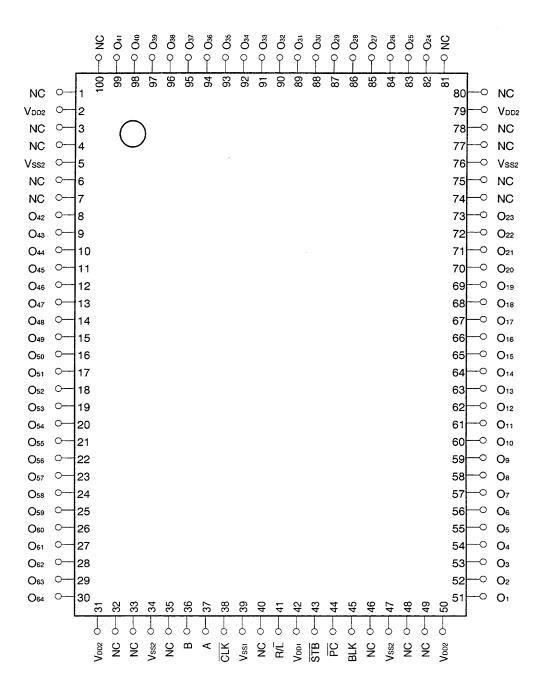

#### PIN CONFIGURATION (Top View)

- Cautions 1. Be sure to leave pin 40 open because it is connected to the lead frame.

- 2. Be sure to use all the V<sub>DD1</sub>, V<sub>DD2</sub>, V<sub>SS1</sub>, and V<sub>SS2</sub> pins. Keep the V<sub>SS1</sub> and V<sub>SS2</sub> pins at the same voltage level.

- Supply power to V<sub>DD1</sub>, logic inputs, and V<sub>DD2</sub> in this order to protect the device from destruction due to latch up. Turn off power in the reverse order.

Observe these power sequences even during a transition period.

#### **PIN FUNCTIONS**

| Pin Symbol       | Pin Name                      | Pin Number                                                                | Remark                                                                                                                                                                   |

|------------------|-------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC               | Polarity reverse input        | 44                                                                        | PC = L: Reverses polarities of all outputs                                                                                                                               |

| BLK              | Blank input                   | 45                                                                        | BLK = H: All outputs = H or L                                                                                                                                            |

| STB              | Latch strobe input            | 43                                                                        | Through at L, holds data at H                                                                                                                                            |

| Α                | RIGHT data I/O                | 37                                                                        | $R/\overline{L} = H$ : A input, B output                                                                                                                                 |

| В                | LEFT data I/O                 | 36                                                                        | R/L = L: B input, A output                                                                                                                                               |

| CLK              | Clock input                   | 38                                                                        | Executes shift at falling edge                                                                                                                                           |

| R/Ū              | Shift direction control input | 41                                                                        | Right shift mode at H A $\rightarrow$ O <sub>1</sub> O <sub>64</sub> $\rightarrow$ B Left shift mode at L B $\rightarrow$ O <sub>64</sub> O <sub>1</sub> $\rightarrow$ A |

| O1 to O64        | High-voltage output           | 51 to 73, 82 to 99, 8 to 30                                               | 80 V 25 mA <sub>MAX</sub> .                                                                                                                                              |

| VDD1             | Logic power supply            | 42                                                                        | 5 V ± 10 %                                                                                                                                                               |

| V <sub>DD2</sub> | Driver power supply           | 2, 31, 50, 79                                                             | 10 to 70 V                                                                                                                                                               |

| Vss1             | Logic ground                  | 39                                                                        | Connected to GND of system                                                                                                                                               |

| Vss2             | Power ground                  | 5, 34, 47, 76                                                             | Connected to GND of system                                                                                                                                               |

| NC               | Vacant pin                    | 1, 3, 4, 6, 7, 32, 33, 35, 40, 46,<br>48, 49, 74, 75, 77, 78, 80, 81, 100 | No connection.  Be sure to leave pin 40 open.                                                                                                                            |

#### TRUTH TABLE 1 (SHIFT REGISTER)

| In  | put      | 1/0           |               | Chiff Dogistor |

|-----|----------|---------------|---------------|----------------|

| R/L | CLK      | A B           |               | Shift Register |

| Н   | <b>\</b> | Input         | Output Note 1 | Right shift    |

| Н   | H or L   |               | Output        | Hold           |

| L   | <b>↓</b> | Output Note 2 | Input         | Left shift     |

| L   | H or L   | Output        |               | Hold           |

Notes 1. S<sub>63</sub> is shifted to the position of S<sub>64</sub> and output from B at the falling edge of the clock.

2.  $S_2$  is shifted to the position of  $S_1$  and output from A at the falling edge of the clock.

## TRUTH TABLE 2 (LATCH AND DRIVER)

|       | In  | out |    | Driver Output Stage                                        |  |

|-------|-----|-----|----|------------------------------------------------------------|--|

| A (B) | STB | BLK | PC |                                                            |  |

| Х     | Х   | Н   | Н  | H (all drivers: H)                                         |  |

| Х     | Х   | Н   | L  | L (all drivers: L)                                         |  |

| Н     | L   | L   | Н  | Н                                                          |  |

| Н     | L   |     | L  | L                                                          |  |

| L     | L   | ١   | Н  | L                                                          |  |

| L     | Ļ   | اد  | L  | Н                                                          |  |

| X     | Н   | اد  | Н  | Outputs data immediately before STB goes to H              |  |

| X     | Н   | L   | L  | Reverses and outputs data immediately before STB goes to H |  |

**Remark** X = H or L, H = high level, L = low level

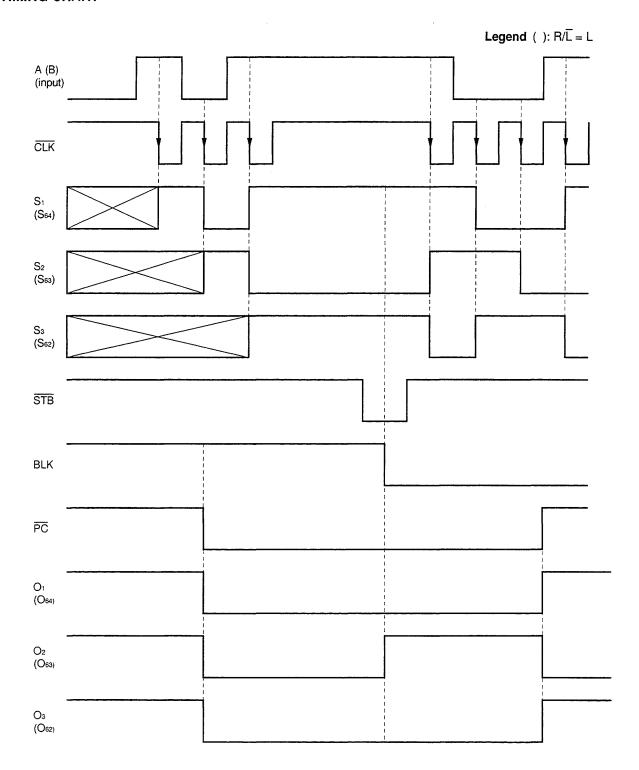

# **TIMING CHART**

# ABSOLUTE MAXIMUM RATINGS (TA = 25 °C, Vss1 = Vss2 = 0 V)

| Parameter                       | Symbol           | Rating                         | Unit |

|---------------------------------|------------------|--------------------------------|------|

| Logic supply voltage            | V <sub>DD1</sub> | -0.5 to + 7.0                  | V    |

| Logic input voltage             | V <sub>1</sub>   | -0.5 to V <sub>DD1</sub> + 0.5 | V    |

| Logic output voltage            | Vo1              | -0.5 to V <sub>DD1</sub> + 0.5 | V    |

| Driver supply voltage           | V <sub>DD2</sub> | -0.5 to 80                     | V    |

| Driver output voltage           | V <sub>02</sub>  | -0.5 to V <sub>DD2</sub> + 0.5 | V    |

| Driver output current           | l <sub>02</sub>  | ± 25                           | mA   |

| Permissible package dissipation | P□               | 1000                           | mW   |

| Operating temperature range     | Ta               | -40 to +85                     | .€   |

| Storage temperature range       | Tstg.            | -65 to +150                    | °C   |

# RECOMMENDED OPERATING RANGE (TA = -40 to 85 °C, Vss1 = Vss2 = 0 V)

| Parameter                | Symbol           | MIN.       | TYP. | MAX.                   | Unit |

|--------------------------|------------------|------------|------|------------------------|------|

| Logic supply voltage     | VDD1             | 4.5        | 5.0  | 5.5                    | V    |

| High-level input voltage | ViH              | 0.7 • VDD1 |      | VDD1                   | V    |

| Low-level input voltage  | Vıl              | 0          |      | 0.2 • V <sub>DD1</sub> | V    |

| Driver supply voltage    | V <sub>DD2</sub> | 10         |      | 70                     | V    |

| Driver output current    | lo <sub>L2</sub> |            |      | +20                    | mA   |

|                          | Гон2             |            |      | -20                    | mA   |

# ELECTRICAL CHARACTERISTICS (TA = 25 °C, VDD1 = 5.0 V, VDD2 = 70 V, VSS1 = VSS2 = 0 V)

| Parameter                  | Symbol            | Conditions                                                   | MIN.       | TYP. | MAX.                   | Unit |

|----------------------------|-------------------|--------------------------------------------------------------|------------|------|------------------------|------|

| High-level output voltage  | Voн1              | Logic IoH1 = -1.0 mA                                         | 0.9 • VDD1 |      |                        | V    |

| Low-level output voltage   | V <sub>OL1</sub>  | Logic lo <sub>L1</sub> = 1.0 mA                              |            |      | 0.1 • V <sub>DD1</sub> | ٧    |

| High-level output voltage  | V <sub>OH21</sub> | O1 to O64, IOH2 = -0.5 mA                                    | 69         |      |                        | V    |

|                            | V <sub>OH22</sub> | O1 to O64, IOH2 = -5.0 mA                                    | 65         |      |                        | V    |

| Low-level output voltage   | VOL21             | O1 to O64, IoL2 = 2.5 mA                                     |            | _    | 1.0                    | V    |

|                            | Vol22             | O <sub>1</sub> to O <sub>64</sub> , I <sub>OL2</sub> = 20 mA |            |      | 10                     | V    |

| High-level input current   | Ін                | Vi = VDD1                                                    |            |      | 1.0                    | μΑ   |

| Low-level input current    | lic               | Vt = 0 V                                                     |            |      | -1.0                   | μΑ   |

| High-level input voltage   | ViH               |                                                              | 0.7 • VDD1 |      |                        | V    |

| Low-level input voltage    | Vil               |                                                              |            |      | 0.2 • V <sub>DD1</sub> | V    |

| Static current dissipation | IDD1              | Logic, T <sub>A</sub> = 25 °C                                |            |      | 10                     | μА   |

|                            | 1001              | Logic, T <sub>A</sub> = -40 to +85 °C                        |            |      | 100                    | μΑ   |

|                            | loo2              | Driver, T <sub>A</sub> = 25 °C                               |            |      | 100                    | μΑ   |

|                            | I <sub>DD2</sub>  | Driver, T <sub>A</sub> = -40 to +85 °C                       |            |      | 1000                   | μΑ   |

6

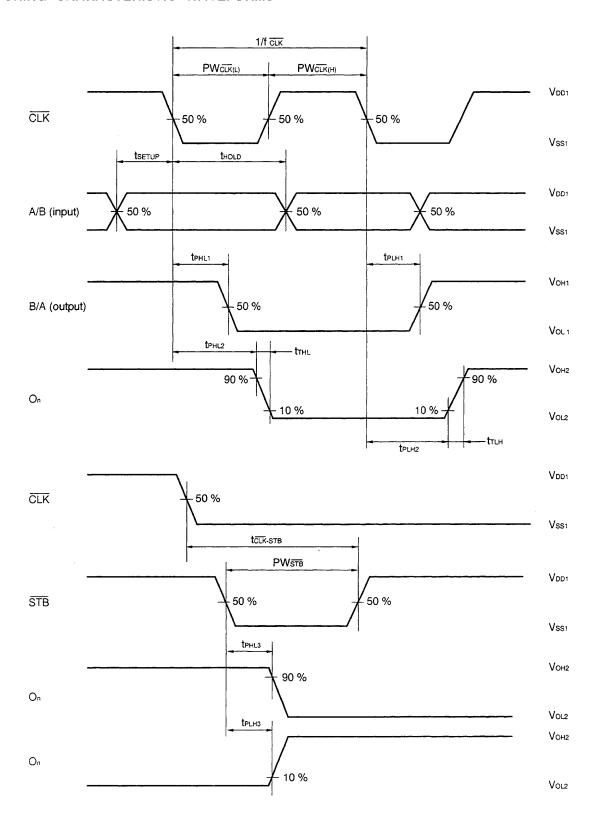

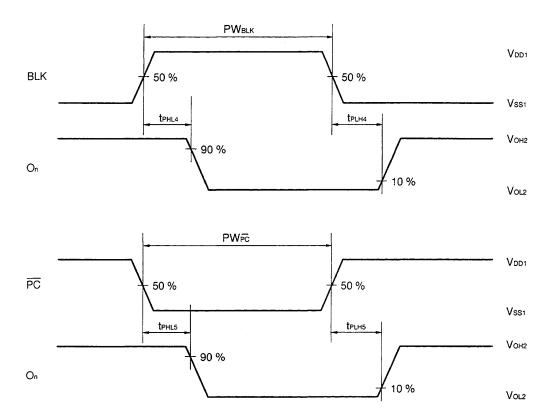

## SWITCHING CHARACTERISTICS

$(T_A = 25 \, ^{\circ}C, \, V_{DD1} = 5.0 \, V, \, V_{DD2} = 70 \, V, \, V_{SS1} = V_{SS2} = 0 \, V, \, logic \, C_L = 15 \, pF, \, driver \, C_L = 50 \, pF)$

| Parameter               | Symbol             | Conditions                                  | MIN. | TYP. | MAX. | Unit |

|-------------------------|--------------------|---------------------------------------------|------|------|------|------|

| Propagation delay time  | tPHL1              | $\overline{\text{CLK}} \to \text{A/B}$      |      |      | 50   | ns   |

|                         | tplH1              |                                             |      |      | 50   | ns   |

|                         | tpHL2              | CLK → O₁ to O64                             |      |      | 300  | ns   |

|                         | tplH2              |                                             |      |      | 300  | ns   |

|                         | tрньз              | STB → O₁ to O64                             |      |      | 300  | ns   |

|                         | tplH3              |                                             |      |      | 300  | ns   |

|                         | ₹PHL4              | BLK → O1 to O64                             |      |      | 300  | ns   |

|                         | tplH4              |                                             |      |      | 300  | ns   |

|                         | t <sub>PHL5</sub>  | $\overline{PC} \rightarrow O_1$ to $O_{64}$ |      |      | 300  | ns   |

|                         | telhs              |                                             |      |      | 300  | ns   |

| Rise time               | tтин               | O1 to O64                                   |      |      | 200  | ns   |

| Fall time               | tтнL               | O1 to O64                                   |      |      | 200  | ns   |

| Maximum clock frequency | f <sub>max</sub> . | Duty = 50%, data loading                    | 25   |      |      | MHz  |

|                         |                    | In cascade connection                       | 16   |      |      | MHz  |

| Input capacitance       | Cı                 |                                             |      |      | 20   | pF   |

## TIMING REQUIREMENTS

(TA = -40 to 85 °C, VDD1 = 4.5 to 5.5 V, VDD2 = 10 to 70 V, Vss1 = Vss2 = 0 V)

| Parameter          | Symbol           | Conditions   | MIN. | TYP. | MAX. | Unit |

|--------------------|------------------|--------------|------|------|------|------|

| Clock pulse width  | PWclk            |              | 20   |      |      | ns   |

| Strobe pulse width | PWsTB            |              | 20   |      |      | ns   |

| Blank pulse width  | PWBLK            |              | 560  |      |      | ns   |

| PC pulse width     | PW <del>FC</del> |              | 560  |      |      | ns   |

| Data setup time    | tsetup           |              | 10   |      |      | ns   |

| Data hold time     | thold            |              | 10   |      |      | ns   |

| Clock-strobe time  | tCLK-STB         | CLK ↓ → STB↑ | 50   |      |      | ns   |

## SWITCHING CHARACTERISTIC WAVEFORMS

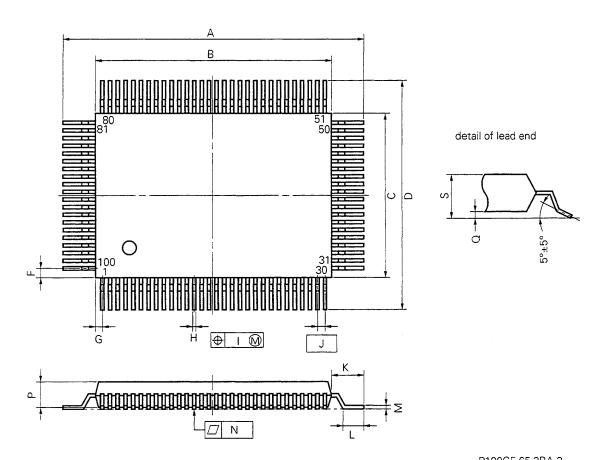

# PACKAGE DRAWING $\mu$ PD16306AGF-3BA (Iron lead frame) 100 PIN PLASTIC QFP (14×20)

#### NOTE

Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition.

|      |             | P100GF-65-3BA-2 |

|------|-------------|-----------------|

| ITEM | MILLIMETERS | INCHES          |

| Α    | 23.6±0.4    | 0.929±0.016     |

| В    | 20.0±0.2    | 0.795+0.009     |

| С    | 14.0±0.2    | 0.551+0.009     |

| D    | 17.6±0.4    | 0.693±0.016     |

| F    | 0.8         | 0.031           |

| G    | 0.6         | 0.024           |

| Н    | 0.30±0.10   | 0.012+0.004     |

| ı    | 0.15        | 0.006           |

| J    | 0.65 (T.P.) | 0.026 (T.P.)    |

| K    | 1.8±0.2     | 0.071+0.008     |

| L    | 0.8±0.2     | 0.031+0.009     |

| М    | 0.15+0.10   | 0.006+0.004     |

| Ν    | 0.15        | 0.006           |

| Р    | 2.7         | 0.106           |

| Q    | 0.1±0.1     | 0.004±0.004     |

| S    | 3.0 MAX.    | 0.119 MAX.      |

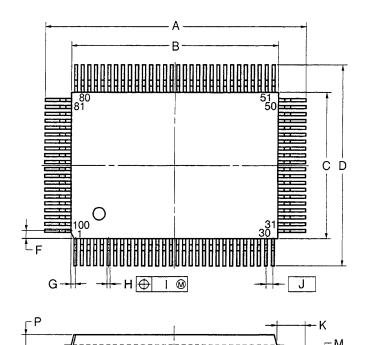

# PACKAGE DRAWING $\mu$ PD16306AGF-3RA (Copper lead frame) 100 PIN PLASTIC QFP (14×20)

detail of lead end

## NOTE

Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS                    | INCHES                                    |

|------|--------------------------------|-------------------------------------------|

| Α    | 23.2±0.2                       | 0.913+0.009                               |

| В    | 20.0±0.2                       | 0.787 <sup>+0.009</sup><br>-0.008         |

| С    | 14.0±0.2                       | 0.551 <sup>+0.009</sup> <sub>-0.008</sub> |

| D    | 17.2±0.2                       | 0.677±0.008                               |

| F    | 0.8                            | 0.031                                     |

| G    | 0.6                            | 0.024                                     |

| Н    | 0.30±0.10                      | 0.012+0.004                               |

| 1    | 0.15                           | 0.006                                     |

| J    | 0.65 (T.P.)                    | 0.026 (T.P.)                              |

| K    | 1.6±0.2                        | 0.063±0.008                               |

| L    | 0.8±0.2                        | $0.031^{+0.009}_{-0.008}$                 |

| М    | 0.15 <sup>+0.10</sup><br>-0.05 | 0.006+0.004                               |

| N    | 0.10                           | 0.004                                     |

| Р    | 2.7                            | 0.106                                     |

| Q    | 0.125±0.075                    | 0.005±0.003                               |

| R    | 5°±5°                          | 5°±5°                                     |

| S    | 3.0 MAX.                       | 0.119 MAX.                                |

S100GF-65-3BA-3

#### RECOMMENDED SOLDERING CONDITIONS

Please perform the soldered mounting of this product under the following recommended conditions.

For soldering methods and conditions other than those recommended here, please contact your NEC sales representative.

#### **Surface Mount Type**

For details on recommended soldering conditions, please refer to the "Semiconductor Device Mounting Technology Manual" (C10535E).

#### $\mu$ PD16306AGF-3BA

| Soldering Method | Soldering Conditions                                                                                                           | Recommended Conditions<br>Symbol |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Infrared Reflow  | Package peak temperature: 235 °C, time: up to 30 sec. (no less than 210 °C), count: once, restricted number of days: none Note | IR-35-00-1                       |

| VPS              | Package peak temperature: 215 °C, time: up to 40 sec. (no less than 200 °C), count: once, restricted number of days: none Note | VP15-00-1                        |

| Pin Part Heating | Pin part temperature: no more than 300 °C, time: up to 10 sec., restricted number of days: none Note                           |                                  |

**Note** This refers to the restricted number of days for storage after decapsulating the dry pack. The storage conditions are no more than 25 °C and 65 % RH.

Caution Please avoid mixing use of soldering methods (except for pin part heating methods).

#### References

NEC Semiconductor Device Reliability/Quality Control System (IEI-1212)

Quality Grades of NEC Semiconductor Devices (IEI-1209)

Semiconductor Device Mounting Technology Manual (C10535E)

[MEMO]

[MEMO]

[MEMO]