Fórum témák

» Több friss téma |

Fórum » Proteus

Sziasztok

Szeretnék segítséget kérni kipróbáltam itt a fórumon közölt DCF77 szinkronizációhoz szükséges file-t, és olvastam hogy működjön invertálni kell a bejövő DCF jelet, tudna nekem valaki segíteni hogy hogyan is fordítsam meg a jelet?

Ráteszel egy NPN tranzisztort egy 1k ohm os bázisellenállással. A kollektora meg egy 470 ohm-on keresztül a +5V-ra. Emitter a testen. Most (közvetlenül) a kollektorról már az invertál jelet veszed le.

Üdv.

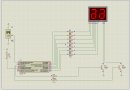

Egy kis segítséget kérnék, hogy a kapcsolásomban a tranzisztorok miért nem működnek úgy, ahogy azt kellene? Látszik is a kijelzőn, hogy mind a 2 olyan mint, ha folyton nyitva lenne. Kösz.

A kijelző milyen (CC vagy CA)?

Közös katód. Kipróbáltam más 7 szegmenses kijelzőkkel is, mindegyikkel egy kicsit máshogy rossz. A vicc az, hogy tegnap megcsináltam már ezt közös anódosra és az működött.

Szeretném majd ezt megépíteni és azért jó lenne előtte kipróbálni, hogy tényleg jó-e.

Ahh, a közös anódoshoz való számok voltak a progiban. Tegnap este ezek szerint nem úgy hagytam, ahogy emlékeztem rá. Viszont a felhúzóellenállások tényleg kellettek, ez volt az alapprobléma.

Köszönöm a segítséget.

Közös katódosnál, kollektor testre, emiter a kijelzöre, bázis PIC-re. A tranyó meg 2n3906. Próbáld meg így, nekem ment.

Üdv!

Az előző problémára úgy hiszem rájöttem, most viszont az érdekelne, hogy a grafikonon az erősítés csökkenő részét milyen kapcsolástechnikával lehetne lineárisabbá tenni. Az lenne a cél, hogy a teljes frekvencián közel egyforma legyen az erősítés.

Mármint csak SMD-et? Olyat már csináltam amin nem volt egy furat sem, hanem minden SMD volt (csatik, IC-k, stb.).

Még nem csináltam furatgalvánt, bár egyszer próbálkoztam kevés sikerrel. Szerintem ha nincs sok furat rajzold át sima körrel öket. Bár ez egy kicsit macerás.

Most csináltam egy új DIL8-as IC-t, olyan PAD-el amibe nincs lyuk.(levettem a Drill hole-t 0-ra) Kinyomtattam PDF-be és belerakta a furatot a szemé... Hogy mért rakta bele azt nem tudom.

Nálam a 7.5-ös verziónál rendben van. Ha a drill mark-ot 0-ra veszem, akkor nem tesz lyukat a rajzra.

(A drill hole a furatrajzhoz ill. gerberhez kell, a rajzolatnál viszont a drill mark fog érvényesülni.)

Igen, miután leírtam Én is rájöttem a tévedésemre, és nálam se tesz lyukat, csak valamiért nem jelenik meg a forrszem, de ez valami grfikus hiba. Amúgy Én a 7.8 sp2-vel próbáltam.

Nem sajnos. Kirakom PDF-be utána Ai (adobe illustrator).

Egy nagyobb panelnál elég időigényes munka lenne. (Azért a gyártó igazán gondolhatott volan ilyesmire.)

Én egy hónapja küzdök a FET-es H-híd szimulációval és nem jutok egyről a kettőre. (hiba hiba hiba) Szép munka gratulálok hozzá.

Szia !

Kis segítség kellene, csatoltam egy egyszerű kapcsolást aminek a kimeneteit szeretném megjeleníteni valami grafikon...stb formában. (nem szkopon akarom nézni) Másik alap dolog amire szintén nem jöttem rá, szimulációkor kerestem elektrolit kondit ami nem volt működőképes "CAP-ELEC" , aztán olyant találtam amiről nem lehet megállapítani melyik melyik fele,"CAPACITOR" az működött a kapcsolásba, utána találtam még a "CAP-POL" -t ami meg mindegy hogyan teszem a kapcsolásba igy is -úgy is működik. Mi akkor az igazság mindegy melyik kondit használom függetlenül a valóságtól

Lehet, hogy már úgy elállítottam a szimulációs beállításokat, hogy ez sem csinál semmit. Próbáltam úgy is, hogy visszaállítok mindent defaultba, de semmi sikerélmény, a voltmérő csak 0-t mutat. Az érdekes, hogy csináltam egy tranyósat és azzal semi probléma nincs.

Amúgy ennél is a hiba a SPICE, Gmin stepper és hiába állítom mindig ugyan az. Vagy a progiba nincs jól beállítva valami, vagy bennem nem jó valami  . .

Szia !

DSN fájl csatolva.

Nincs benne TC4469. Vagy milyen szimulációs fájl?

Csináltam egy másik hidat ami összerakva szépen megy az asztalon, kb 25 amperig terheltem és a FET-ek hidegek maradtak, de a szimulátorba nem megy és ez nagyon zavar, mert tovább szeretnék kisérletezni vele, de nem szeretnék kukába dobálni alkatrészeket.

Bocsi lemaradt. Ha a híd egyik bemenetére 5 volt a másikra GND úgy is mennie kéne, de itt a HEX is.

A hídépítés közben azt szeretném megkérdezni, hogy a munkalap méretét hol lehet megnövelni, ha nem fér bele a kapcsolás?

Ha esetleg valakit érdekel az uc3842 felrakom ide. Elméletileg szimulálható, Én most tesztelem.

Itt egy digitális analízis a kapcsolásodról.

Szia !

Köszi  Már csak az a kérdés nekem miért nem sikerül létrehoznom. Ahogy próbálom: kimenetekre leteszem az OUT-t kiteszem a digital analysis-t OUT nyilakat megfogva ráhúzom az analysis-re. Utána lesznek vízszintes vonalak és annyi.....

Üdv!

Az edit graph menüben be kell állítani, hogy mennyi időt analizáljon. Ha ezt kicsire választottad, akkor alacsony frekvenciánál nem történik az áramkörben még semmi változás a kimeneten és nem is tud mit regisztrálni.

Meg lett a megoldás, a potit kellett közép irányba állítani egy kicsit. Köszi !

|

Bejelentkezés

Hirdetés |