Fórum témák

» Több friss téma |

Milyen q's lábra gondolsz te? Nincs is olyan elnevezésű láb az IC-n. Pontosíts kérlek...!

De hogyan? nekem volt olyan kapcsolásom ami pont az elégtelen keresztmetszetű /túl hosszú test miatt nem működött jól .(és nem a rajta eső veszteség miatt)

Nincs külön szintillesztés. PLC 24V kimenő jele megy az optóra, az meg kapcsol a Shift regiszternek 5V-okat.

Mit értesz hiszterézises bemeneti tagon, meg mi lenne a szerepe az integráló tagnak? Hogy gondoltad a megfeleő számú léptető órajel számolását? És hogy történne az IC törlése? Ha törénik egy adatkiküldés, akkor utána törlődik, vagy ha nem is törlődik, akkor Q0-ról kezdi a következő adat beolvasást, shiftelést. Sajnos már nem áll módomban más IC használata, mert már kész a panel meg megvan az IC. Már csak helyes működésre kell ösztönözni.

A PLC tápja és az 5V-os táp egy kb. fél méteres vezetékkel össze van kötve (föld közösítés céllal).

Ez egy F-es, azaz fast (gyors) IC, ha belenéztél az adatlapba, akkor láthattad, hogy pár ns-os idők vannak megadva mindenhol minimumnak. Kicsit vicces lenne, ha a 40MHz sok lenne neki (ráadásul egy 40MHz-en járó PIC-ből legjobb esetben is 10MHz gyorsaságú jelet bírsz programmal kiküldeni).

A másik kérdés az áramfelvétel. Igen, a gyors IC-k kifejezetten sokat esznek, tehát simán lehet normális a 110mA-es áramfelvétel, mint ahogy illeszkedik is az adatlapban megadott tartományba.

A PCL-nek milyen kimenete van? Egy F-es IC-nél a jelváltásnál fellépő esetleges gyors rezgések is simán jelentkezhetnek zavarként. Milyen hosszú kábelen keresztül kapja a jelet az IC a PLC-ből?

Ne keverd már a szezont a fazonnal, légy szíves! Ott van az adatlapban fehéren-feketén, hogy mi a tipikus és a maximális áramfelvétele az IC-nek. A peremfeltétel is körül van írva a két sorhoz: az egyikben a kimenetek H állapotúak, a másikban L állapotúek. Nincs sehol semmi írva arról, hogy akármennyivel terhelve lennének a kimenetek. Ez az IC saját fogyasztása.

Jelenleg a PLC és a panel közti kommunikációs kábel hossza kb. fél vagy talán egy méter. Viszont, ha a végleges beépítési helyére kerül ott lesz 5 méter is a távolság.

Mit értesz azon, hogy milyen kimenete van a PLC-nek?

Ha magas szintű, akkor 24V, ha alacsony szintű, akkor aktív alacsony (testre van húzva egy ellenállással) nem leveg, ha erre gondoltál.

Azt hiszem, nem vagy tisztában a shift regiszter működési elvével.

Itt nem arról van szó, hogy "a Q0-tól kezdi a beírást", hanem arról, hogy van egy 16 bites szó, aminek az összes bitjét eggyel eltolod, és az újonnan beérkező bit bekerül a Q0-ba. Azaz az első impulzus után megjelenik a korábbi Q14 állapota a Q15-ön, a korábbi Q13 állapota a Q14-en ... a korábbi Q0 állapota a Q1-en, és a beíró bit korábbi állapota a Q0-n. A "korábbi állapot" a léptető impulzus előtti állapot. Mivel ennek az IC-nek nincs törlési funkciója, csak úgy tudod előállítani az összes kimenet L állapotát, ha "beletolsz" 16 db L állapotot a léptetőregiszterbe. Ennél a típusnál még annyival van kiegészítve a fent leírt működés, hogy a léptetőregiszter kimenetei és az IC kimeneti lábai között van egy közbülső tároló, amibe a beírást külön tudod vezérelni. Ezzel az érhető el, hogy a léptetőregiszterbe egy teljesen új 16 bites szót is be tudsz írni úgy, hogy a kimenetek nem változnak, majd az összes kimeneti láb állapota egyszerre változtatható meg az új értékekre.

Ez egy TTL IC, ráadásul gyors működésú. Ilyen távolságokra (már a fél méterre is), főleg kábeles, nem fixre szerelt körülményekhez mindenképpen kell valami illesztő illetve jelformáló megoldás. Ha nincs, akkor olyan bizonytalanságok lesznek a rendszerben, mint amit meg is tapasztalhattál.

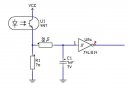

Valaki korábban említette a tápfesz zavarszűrését, az is nagyon fontos. Az IC környékére érdemes valami pártíz µF elkót (tantál) elhelyezni, főleg, ha távolabbról jön a tápfesz és nem ott van előállítva a paneljén, valamint kötelező közvetlenül az IC táplábainál, minél rövidebb vezetékezéssel elhelyezni 1-200nF értékű kermia (vagy más, olyan típusú kondenzátor, aminek a saját induktivitása minimális) hidegítést. Nagy sebességű IC-knél ezt nem lehet megspórolni. Jelformálásnak én is RC tagos integrálótagot és Schmitt triggeres kapukat tennék a léptetőregiszter bemenetei elé.

Igen, erre voltam kíváncsi, közben láttam is a rajzot, ha az van megépítve.

Nos, az úgy szerintem nagyon nem jó. Bár az ellenállásértékeket nem látom, de ebben az elrendezésben pártíz ohmig le kellene menni, hogy kevésbé legyen zavarérzékeny. Akkor már jobb elrendezés lenne, ha az optók tranzisztorai a földön ülnének és a föld felé húznák a bemeneteket, az ellenállások pedig a táp felé húznák fel azokat. Oda akkor 3-400 ohm lenne talán célszerű.

Erről beszéltem már, csak közben elment másra az időm...

Triggernek berakhatsz 1 db 74LS14-et ( 6 db), de a működési fázist meg kell fordítani.... 1>0, 0>1 a bemeneten pl., vagy mint proli007 mondta, átforgatod az opto-tranyókat.

Integrálni eléje meg 1k-100...220 pF ( a bejövő jel-frekitől-gyorsaságtól függően, aztán ránöveszted a fő-panelre...).

Ezen a mondatodon mit értesz "ha én ténylegesen a 16 jel beküldése után teszem ezt meg, akkor ha csak egy magas szintű jelet töltök bele a Q0-as kimenetbe ő akkor is több lábra kiteszi." Milyen adatokat küldesz be és hol? Ha a beléptetett illetve régebben beléptetett értékek között több 1 van akkor jogos a működése.

Szia!

Idézet: „Nincs külön szintillesztés. PLC 24V kimenő jele megy az optóra, az meg kapcsol a Shift regiszternek 5V-okat. ” Hát maga az opto adj a szintillesztést, hiszen a PLC kimenete 0/24V a TTL bemenete 0/5V. Idézet: „Mit értesz hiszterézises bemeneti tagon, meg mi lenne a szerepe az integráló tagnak? ” Fercivel egy órajelre jár az agyunk.  A mellékelt rajzon láthatod. Ha az invertálás zavar, akkor az Optot és az alatta lévő ellenállást megfordíthatod. A mellékelt rajzon láthatod. Ha az invertálás zavar, akkor az Optot és az alatta lévő ellenállást megfordíthatod.Az integráló tagnak a szerepe, az esetleges zavarjelek kiszűrése. A hiszterézises inverter, meg növeli a zavarsávot, és vissza állítja a jel meredekségét. (Ezt akkor is alkalmaznám, ha nem használnák integráló tagot.) Idézet: „Hogy gondoltad a megfeleő számú léptető órajel számolását? És hogy történne az IC törlése? Ha törénik egy adatkiküldés, akkor utána törlődik, vagy ha nem is törlődik, akkor Q0-ról kezdi a következő adat beolvasást, shiftelést. ” Megrajzolnám mire gondoltam, csak értelme nem volna, ha azt mondod, hogy "már kész a panel meg megvan az IC". Egyébként, az -SHCP jeleket számolnám és megnézném, hogy az adatátviteli idő alatt, eléri-e a 16-ot. Ha nem, akkor hibás az adatsor. Mivel nem lehet egyszerűen törölni a shift regiszter, 16db nullát léptetnék be. Tehát a SI vonal alacsony állapotában, 16db órajelet generálnák az -SHCP bemneten. Persze ez egy kalap IC-t jelentene plusz ban. Így továbbra is fenntartom a véleményem, hogy ha adatellenőrzést is szeretnél, azt nem érdemes diszkrét elemekből építeni. Amúgy az adatátvitel biztonságát, Én úgy oldanám meg a helyedben, hogy visszaolvasnám a PLC-re a kivitt adatot, és ha egyezik, csak akkor másolnám be a kimenetre. (persze nem ezzel az IC-vel) akkor a PLC eldönthetné, mi legyen. (A jó öreg ECHO!) Egyébként eldönthető, hogy a 16db kimenet milyen állapotot vegyen fel, ha az adatátvitel hibás? (Amúgy Szilvának igaza van, gondold át a regiszter működését. Mert hozzászólásaid alapján az látszik, hogy nem tiszta. Mert ilyen nincs hogy innen kezdi, meg onnan kezdi. Ez egy FiFo regiszter, ez csak taszigálja a jelet befelé, az órajel ütemében.) A PLC működtető diagramját közre adhattad volna, akkor kiderült volna a segítőknek néhány dolog, pld. hogy mit teszel rosszul a vezérlésnél. (Azt pld. figyelembe vetted, hogy a kimeneteit kb. 100msec-onként írja megés egyszerre, ha jól emlékszem?) Ha optocsatolót alkalmazol, akkor miért kell közösíteni a tápfeszt? Akkor egy sima feszültségosztó egy zénerrel is megtette volna. De jó az opto, csak a földelések kialakítását (vezetékelés-táp) ki kell agyalni. Bocs, ha számodra triviálisakat írok. üdv! proli007

szia

hát szerintem pedig van  Q's 10 láb! Qs 9 láb az késleltetett jelet ad tovább.... Az csúszást okoz a léptetésben. Mondjuk én pic-el csinaltam plc  4x20 kijelző 16 bemenet cd4067 ebből 4 optos illesztéssel 16 Fetes Kimenet 2db cd4094 meghajtásnak pár lehetőség még...  4094-es panelt mellékeltem. amugy sima dip24 felelmeg,vasalással is simán jó majd teljes vezérlésről rakok fel képeket, majd nem kész vagyok vele...

Hello

Építettem egy LED kijelzős órát, de kevesebb lábú PIC-re szeretném átírni a programját. Olvastam Vicsys kolléga kapcsolását, láttam hogy ő 74LS164 IC-vel oldja meg a kijelző vezérlését. Én is ezt az IC-t szeretném használni, de nem tudom, hogy hogy kell vezérelni. Adatlapja se segített túl sokat. Azt látom, hogy a kapcsolásban a két adatbemenet láb össze van kötve, és ezenkívül az órajel láb van még a PIC-re kötve. El tudná valaki magyarázni, hogy hogy kell kiküldeni 1 byte-ot a shiftregiszternek, hogy aztán aszerint tudja a kimeneteit ki- bekapcsolni? Üdv. és előre is köszönöm

Az IC-nek van egy törlő bemenete is (minden kimenetet alacsony állapotba ír), de ez nincs használatban.Mivel negált bemenet, magas szintre kell kötni, hogy ne zavarjon. Én azért betettem volna egy 1-10 kOhm-os soros ellenállást...

Az adatbemenet (összekötve) egy PIC kimenetre kötendő. Oda kell kiadni a soron következő adatbitet (BSF/BCF utasítással), majd az órejel bemenetet vezérlő PIC lábon egy impulzust kell kiadni (kimenetet magas szintre állítani, majd alacsonyra). Minden ilyen óraimpulzus egy bittel orébblépteti a shift regiszterben az adatokat (tehát Q6 -> Q7, Q5 -> Q6, Q4 -> Q5, Q3 -> Q4, Q2 -> Q3, Q1 -> Q2, Q0 -> Q1 és AB -> Q0). 1. Kell tehát szervezni egy ciklust, 1-től 8-ig. 2. Elő kell venni az adatot (mondjuk W-be) 3. Egy balraforgatás C (STATUS egyik bitje) írja D7-et 4. Ha C=1 akkor az adatkimeneti lábat 1-be kell állítani 5. Ha C=0 akkor az adatkimeneti lábat 0-ba kell állítani 6. Az órajel kimneten egy impulzust kell kiadni 7. Ciklusszámlálás. Ha még nem járt le a ciklus, akkor ugrás vissza 3-hoz

H van 5 szabad lábad akkor inkább a BCD/7 szegmens dekóderrel csinálnám.Kevésbé macerás.

És ha az IC-re tápot adunk, akkor az összes kimenete először alacsony szintű lesz, vagy érdemes a biztonság kedvéért 0-ra beállítani minden indulás után az összes kimenetet?

Üdv.

Hello

Ott tartok most, hogy próbapanelon összeraktam az áramkörömet, 74LS164-et használtam, az adat bemeneteket összekötöttem és rákötöttem a pic egyik kimenetére. A Clock lábát is rákötöttem a pic egyik kimenetére. Nem működött, olyan volt, mintha a pic nem kapcsolt volna magas szintet az adatemenetekre, pedig kapcsolt. PicKit2-ben van logic analyzer funkció(olyasmi, mintha szkóp lenne, de csak magas és alacsony jelszinteket tud kirajzolni), rákötöttem az egyik csatornáját erre erre az adatbemenet páros + pic kimenet pontra. Észrevettem, hogy nem jelenik meg ott a magas jelszint, amikor a pic magas szintre kapcsolja ezt a pontot. Először azt hittem, hogy a pic programjában rontottam el valamit, de nem. Ezután erről a pontról levettem a pic kimenetét (szóval csak a 74ls164 két adatbemenete maradt összekötve), és egy kilós ellenállással felhúztam ezt a pontot tápra(+5V). Rámértem erre a pontra multiméterrel, és csak kb. 0,3V-ot mértem. Nem jutottam így előbbre, ezért rálestem a 74ls164 adatlapjára, megnéztem, hogy hogy kell bekötni ezeket a lábakat, és az ezenlábakon lévő jelszintváltozások hogyan hatnak a kimenetekre. Láttam, hogy ha az egyik adatbemenetet fixre tápra húzom, és csak a másik adatbemenetet kötöm a picem kimenetére, akkor ugyanaz lesz az egész, ugyanúgy fog viselkedni, mintha össze lenne kötve a két adatbemenet. Így hát az egyik adatbemenetet direktbe tápra kötöttem, szóval soros ellenállás nélkül. Ezután élesztéskor már úgy nézett ki, hogy menni fog, de egyszer csak felmelegedett az ic, a led kijelzőn a világító szegmensek elhalványodtak, majd kialudtak. Hozzáteszem, a 74ls164 kimenete egy ULN2803-as tranzisztormezőt hajtott meg, szóval nem a kimenetén folyhatott nagy áram. A kérdésem az lenne, hogy akkor hogy kell használni ezt az IC-t úgy, hogy ne halálozzon el?  Nem baj, hogy nem 74HC164-et használtam, hanem 74LS164-et? Üdv.

A két testet összekötötted mielőt próbálkoztál volna,valamint mindkét (pic 74hc..) tápja is 5V volt akkor az ic eleve rosz volt.

A felforrás oka a zárlatos bemenet volt amit direkt a tápra kötöttél (esetleg valamit rosszul értelmeztél, és az kimenet volt???) Az LS meg a HC különbség talán az illesztést befolyásolja (a jelszintek nem stimmelnek,bár ez nem okoz ilyen gondot. ) ,esetleg a pic részére jelent plusz terhellést.

Hello

Közös volt a PIC és az IC testje és tápja is. Biztos az egyik bemenetet kötöttem direkt a tápra, nem kimenetet. Az előfordulhat, hogy rossz lehetett az IC, mert ezt még régebben kaptam egy ismerőstől egy csomó más alkatrésszel karöltve, amikor elkezdtem foglalkozni az elektronikával, bár még nem volt beforrasztva, ahogy láttam. Nekem akkor most a HC vagy az LS jelzésű IC kell? Üdv.

Üdv! Nekem a 74HC595 regiszterekkel gyűlt meg a bajom. Az áramkör 3 db reg.-ből(sorba kötve+ULN2803) és egy ATmega16 prociból áll. Az adatlap s rengeteg mintaprogram alapján az adatok beírása így néz ki: clock 0, adat a DS re, clock 1, clock 0. Miután mind a 24 bit ki lett küldve a latch enable-t 1re állítom. A problémát még én sem tudom nagyon jól leírni, egyszerűen néha hibás adat kerül a kimenetekre. Íme néhány teszt:

- ha 24 db 1-t küldök jók a bitek - ha 24 db 0-t jók - ha 1111.0000 1111.0000 1111.0000 az eredmény 1111.1000 1111.0000 1111.0000 - próbáltam más változatokat is (nem jegyeztem le mindet), más helyen is produkálja ugyanezt. Az ULN áramköröknél nem használok felhúzó ellenállást, de gondolom ez nem gond hisz a csupa 0-ra jól működött. Valami ötlet?

Hello!

Úgy látom azt a hibát követed el, hogy nem másolod át a shift regiszter tartalmát, a Latch regiszterbe. Pedig annak tartalma fog a kimenetre kerülni. (Ez biztosítja, hogy az adatok beléptetésekor, a kimenetek ne változzanak.) Tehát az adatok kiléptetése után, a LATCH-CLOCK felfutó élével kell az adatot a kimenetre másolni.. Ha az ULN-t inverternek használod valamely bemenet előtt, (mert nem írtad hova kötötted be) akkor kell felhúzó ellenállás, hiszen az nyitott kollektoros kimenetű. üdv! proli007

Idézet: Sajnos nem az általad leírt dolog a gond. Megpróbálom a felhúzó ellenállásokat bár nem értem hogy miért okozna egyszer egyszer gondot, máskor pedig nem. „Az adatlap s rengeteg mintaprogram alapján az adatok beírása így néz ki: clock 0, adat a DS re, clock 1, clock 0. Miután mind a 24 bit ki lett küldve a latch enable-t 1re állítom.”

Hello!

Bocs, akkor még sem olvastam el elég alaposan.. De még most sem írtad, hol használtad az ULN-t. Egy nyitott kollektoros dolog egy HC bemenetén, nem lehet jó ötlet. Akkor a felhúzó ellenállásokat, csak a védődiódák viszárama biztosítja? (Meg esetleg, hogy nem tudni pontosan mi is van az IC-ben.) Így sebesség függő is lehet a dolog. Apropó próbáltad lelassítani a dolgot? Mert úgy esetleg látod mi zajlik le.. üdv! proli007 |

Bejelentkezés

Hirdetés |